C51单片机通过74HC273控制LED输出实战

C51单片机是基于Intel 8051内核发展而来的一类广泛应用的8位微控制器,以其结构清晰、指令集精炼、成本低廉而广泛应用于工业控制、智能仪表、家电等领域。其核心由CPU、ROM、RAM、定时器/计数器、串口通信模块及多个并行I/O端口组成,具备较强的实时控制能力。74HC273 是 DIP 封装的 20 引脚芯片,其引脚排列如下(从顶部俯视):引脚编号功能描述1Q0 输出2D0 输入3D1 输

简介:本文介绍如何使用C51单片机通过74HC273芯片控制八位LED灯的输出。74HC273是一款8位透明锁存器,适用于数据存储与传输。结合C51编程环境,通过配置单片机并行接口和控制锁存使能信号,实现对LED灯的动态显示控制。文章涵盖硬件连接、程序设计、时序控制等内容,适用于51、96、88系列及ARM架构微控制器的学习与应用。

1. C51单片机简介与开发环境

C51单片机是基于Intel 8051内核发展而来的一类广泛应用的8位微控制器,以其结构清晰、指令集精炼、成本低廉而广泛应用于工业控制、智能仪表、家电等领域。其核心由CPU、ROM、RAM、定时器/计数器、串口通信模块及多个并行I/O端口组成,具备较强的实时控制能力。

1.1 C51单片机的基本结构与功能

C51单片机的内部结构主要包括以下几个核心模块:

- 中央处理器(CPU) :执行指令,进行数据处理。

- 程序存储器(ROM/Flash) :存储用户程序。

- 数据存储器(RAM) :用于变量存储与堆栈操作。

- 定时器/计数器 :实现定时与计数功能,常用于延时或事件计数。

- 串行通信接口(UART) :实现与其他设备的串行数据交换。

- 并行I/O端口(P0~P3) :用于连接外部设备,实现输入输出控制。

其引脚功能丰富,支持多种工作模式,如外部中断、串口通信等。C51系列单片机广泛使用于嵌入式系统的初级开发教学与工业应用中。

1.2 开发环境搭建:Keil μVision配置详解

要进行C51单片机的程序开发,首先需要搭建一个高效的开发环境。Keil μVision 是业界广泛使用的集成开发环境(IDE),它支持C语言开发、调试、仿真等功能,极大提高了开发效率。

安装步骤如下:

- 下载安装包 :从Keil官网或可信来源下载Keil C51版本安装包。

- 运行安装程序 :按照提示选择安装路径和组件(建议勾选C51编译器)。

- 注册许可证 :安装完成后,打开Keil μVision,输入注册码(可通过官网申请评估版)。

- 配置编译器路径 :在菜单栏中选择

Project > Manage > Project Items,确保C51编译器路径正确。

创建第一个C51工程:

- 打开Keil μVision,点击

Project > New μVision Project。 - 输入工程名称,选择目标芯片(如 AT89C51)。

- 添加源文件(

.c或.asm)到Source Group 1。 - 编写简单程序,例如点亮一个LED:

#include <reg51.h>

sbit LED = P1^0; // 定义P1.0为LED控制端

void main() {

while(1) {

LED = 0; // 点亮LED(低电平有效)

}

}

- 点击

Project > Build Target编译工程,确保无错误。 - 点击

Debug > Start/Stop Debug Session进入仿真调试模式。 - 使用

Run按钮运行程序,观察寄存器和I/O口变化。

工程配置注意事项:

- 在

Options for Target中配置晶振频率(通常为12MHz),确保延时函数准确。 - 启用生成HEX文件选项,用于烧录到实际芯片中。

- 可以使用

uVision的逻辑分析仪功能查看I/O信号波形,辅助调试。

本章为后续章节打下了坚实的开发基础,使读者能够在Keil环境下顺利编写和调试C51程序,进而与74HC273等外设芯片进行交互。

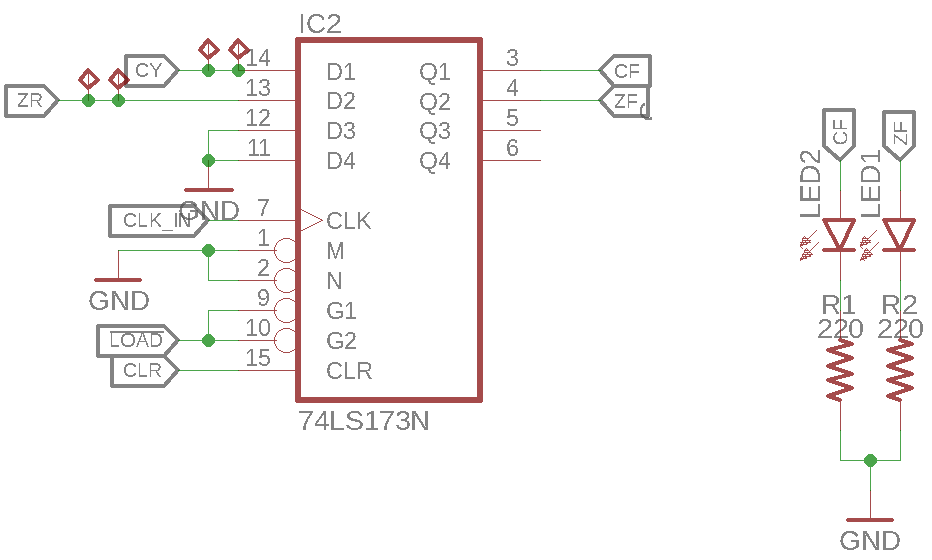

2. 74HC273芯片工作原理

74HC273 是一款常见的高速 CMOS 八位 D 型锁存器芯片,广泛应用于数字系统中作为数据存储和缓冲元件。它具备时钟控制的数据锁存功能,能够将输入数据在时钟信号的上升沿进行锁存,保持输出状态直到下一次时钟触发。本章将深入剖析 74HC273 的基本功能、工作时序及其在数字系统中的典型应用场景,帮助读者理解其内部结构与操作机制,为后续的接口设计与程序控制打下理论基础。

2.1 74HC273芯片的基本功能

74HC273 属于标准的 TTL 兼容 CMOS 逻辑集成电路,具有八个独立的 D 型正边沿触发锁存器。其核心功能是在时钟信号(CLK)的上升沿将输入数据锁存,并在输出端 Q 保持该数据,直到下一次触发。

2.1.1 芯片概述与引脚定义

74HC273 是 DIP 封装的 20 引脚芯片,其引脚排列如下(从顶部俯视):

| 引脚编号 | 功能描述 |

|---|---|

| 1 | Q0 输出 |

| 2 | D0 输入 |

| 3 | D1 输入 |

| 4 | Q1 输出 |

| 5 | D2 输入 |

| 6 | Q2 输出 |

| 7 | GND 地 |

| 8 | Q3 输出 |

| 9 | D3 输入 |

| 10 | D4 输入 |

| 11 | Q4 输出 |

| 12 | D5 输入 |

| 13 | Q5 输出 |

| 14 | VCC 电源(+5V) |

| 15 | D6 输入 |

| 16 | Q6 输出 |

| 17 | D7 输入 |

| 18 | Q7 输出 |

| 19 | CLK 时钟输入 |

| 20 | CLR 清零输入(低电平有效) |

功能说明:

- D0~D7: 数据输入端口,连接输入数据总线。

- Q0~Q7: 数据输出端口,输出锁存后的数据。

- CLK: 时钟信号输入端,上升沿触发数据锁存。

- CLR: 清零信号输入端,低电平有效,用于将所有输出清零。

- VCC 和 GND: 电源和地线,通常为 +5V 和 0V。

2.1.2 锁存器与数据缓冲机制

74HC273 内部集成了八个 D 型触发器,每个触发器在 CLK 上升沿到来时,将对应的 D 输入端的数据锁存到输出 Q。这种锁存机制使得 74HC273 可以作为数据缓冲器使用,将输入数据暂存后稳定输出,避免总线信号的毛刺或干扰影响下游电路。

数据锁存流程如下:

- 当 CLK 为低电平时,D 输入端的数据不被锁存。

- 当 CLK 上升沿到来时,所有 D 输入端的数据被同时锁存到各自的 Q 输出端。

- 即使 D 输入端数据发生变化,只要 CLK 未再次触发,输出 Q 保持不变。

示意图:

graph TD

A[CLK低电平] --> B[等待上升沿]

B --> C{CLK上升沿?}

C -- 是 --> D[锁存D0~D7数据]

C -- 否 --> B

D --> E[保持Q0~Q7输出]

这种锁存机制使得 74HC273 非常适合用于需要同步数据更新的场合,例如 LED 显示控制、并行输出扩展等。

2.2 74HC273的工作时序分析

为了确保 74HC273 正常工作,必须对其工作时序进行精确分析。主要包括数据写入锁存器的建立与保持时间要求,以及控制信号(如 CLK 和 CLR)的配置。

2.2.1 数据写入锁存器的时序要求

在数据写入前,输入数据必须满足建立时间(Setup Time)和保持时间(Hold Time)的要求,以确保在 CLK 上升沿到来时数据稳定。

典型时序参数(以 TI 74HC273 数据手册为例):

| 参数名称 | 定义 | 典型值(ns) |

|---|---|---|

| t_SU | 数据建立时间(CLK 上升沿前) | 10 |

| t_H | 数据保持时间(CLK 上升沿后) | 5 |

| t_PHL | CLK 到 Q 输出延迟 | 12 |

| t_W | CLK 脉冲宽度(高电平持续时间) | 10 |

时序图示意:

sequenceDiagram

participant D as Data Input

participant CLK as Clock

participant Q as Output Q

D->>CLK: Data稳定在CLK上升沿前t_SU

CLK->>CLK: 上升沿触发

CLK->>Q: Q在t_PHL后更新输出

D->>CLK: 数据保持t_H后变化

说明:

- 建立时间 t_SU: 在 CLK 上升沿之前,输入数据必须提前稳定至少 10ns。

- 保持时间 t_H: 在 CLK 上升沿之后,输入数据必须保持稳定至少 5ns。

- CLK 脉冲宽度: CLK 高电平持续时间必须大于 10ns,以确保锁存器正常触发。

2.2.2 控制信号(如CLK、CLR)的作用与配置

CLK(时钟信号):

- 用于触发数据锁存。

- 上升沿有效,下降沿无动作。

- 可由单片机、计数器或外部时钟源提供。

CLR(清零信号):

- 低电平有效,用于将所有输出 Q 清零。

- 若不需要清零功能,可将其上拉至 VCC(+5V)保持高电平无效状态。

配置示例:

// 假设使用单片机控制74HC273

sbit CLK = P3^0; // CLK连接到P3.0

sbit CLR = P3^1; // CLR连接到P3.1

void latch_data(unsigned char data) {

P0 = data; // 将数据写入P0口(连接D0~D7)

CLR = 1; // 清零信号无效

CLK = 0; // CLK初始为低

// 延时确保建立时间

delay_us(1); // 确保数据稳定

CLK = 1; // 上升沿触发锁存

delay_us(1); // 维持CLK高电平时间

CLK = 0; // 恢复低电平

}

代码说明:

P0用于输出数据,对应 74HC273 的 D0~D7 输入。CLK控制锁存触发,通过延时确保符合时序要求。CLR在不需要清零时保持高电平。

2.3 74HC273在数字系统中的典型应用

74HC273 因其锁存功能广泛应用于需要并行数据输出和缓冲的场合。以下是其在数字系统中的两个典型应用:并行输出扩展器和外围设备连接。

2.3.1 作为并行输出扩展器的使用

在单片机系统中,尤其是 C51 系列单片机中,端口资源有限,无法直接驱动多个外设。此时,74HC273 可作为并行输出扩展器,将单片机的一个 8 位数据口扩展为多个独立控制的输出通道。

连接方式:

- 单片机的 P0 口连接到 74HC273 的 D0~D7。

- 单片机的一个 I/O 引脚控制 CLK。

- 多个 74HC273 可并联使用,各自连接不同的 CLK 信号,实现多个输出端口的独立控制。

优点:

- 成本低、电路简单。

- 可扩展性强,支持多级级联。

- 支持快速数据更新与保持。

2.3.2 与其他外围设备的连接方式

74HC273 常用于连接 LED 显示器、数码管、继电器、LCD 屏幕等外围设备。例如,在 LED 显示系统中,74HC273 可用来锁存段码或位选信号,实现稳定显示。

LED 显示连接示例:

| 74HC273 输出 | 连接对象 |

|---|---|

| Q0~Q7 | LED 段码 |

| CLK | 单片机控制时钟 |

| CLR | 可选清零控制 |

动态显示控制流程:

- 单片机将段码数据写入 P0。

- 触发 CLK 上升沿,将段码锁存到 74HC273。

- 将输出连接到 LED 的段选端,点亮对应段。

- 循环扫描多个 LED,实现动态显示。

电路示意图示意:

graph LR

MCU[P0] --> HC273[D0~D7]

MCU[CLK] --> HC273[CLK]

HC273[Q0~Q7] --> LED[段码输入]

LED --> VCC

通过这种方式,74HC273 能够有效扩展单片机的输出能力,并实现对多个外设的高效控制。

3. 74HC273与单片机接口设计

在嵌入式系统中,单片机往往需要扩展外部的数字输出能力,以驱动如LED数码管、继电器、LCD等外设。74HC273作为一款高速CMOS锁存器,具有8位数据锁存功能,能够有效缓解单片机IO口的负载压力,并提供稳定的输出信号。本章将围绕74HC273与C51系列单片机之间的接口设计展开详细讨论,涵盖硬件连接、端口资源分配、地址译码、时序匹配与优化等内容,旨在构建一个高效、稳定的数据输出接口系统。

3.1 硬件连接方案设计

3.1.1 数据总线与地址总线的配置

在C51单片机中,P0口通常作为低8位数据总线(D0~D7)使用,而P2口则作为高8位地址总线(A8~A15)。对于74HC273芯片,其数据输入引脚D0~D7应与单片机的P0口连接,以实现并行数据传输。地址总线则通过译码器(如74LS138)生成片选信号(CS),控制74HC273的选通。

以下是一个典型的硬件连接方案示意图(使用Mermaid绘制):

graph TD

A[C51单片机] -->|P0[0:7]| B[74HC273 D0-D7]

A -->|ALE| C[地址锁存器74HC373]

C -->|A0-A7| B

A -->|WR| D[写控制信号]

D --> B[CLK]

A -->|P2[0:1]| E[地址译码器]

E --> B[CS]

图3.1 74HC273与C51单片机的典型接口结构

该结构通过地址译码器生成74HC273的片选信号,P0口负责数据传输,WR信号控制写入时机,CLK信号则由单片机的写操作触发,实现数据锁存。

3.1.2 控制信号线的连接与逻辑设计

74HC273的关键控制信号包括时钟输入(CLK)、清零(CLR)和输出使能(OE)。其中:

- CLK :上升沿触发数据锁存;

- CLR :高电平有效,清空锁存器内容;

- OE :低电平有效,允许输出。

在实际设计中,通常将CLR接高电平保持无效,OE接地保持输出有效,CLK则由单片机的写信号(WR)控制。具体连接如下:

| 74HC273引脚 | 功能 | 连接对象 |

|---|---|---|

| D0-D7 | 数据输入 | P0口 |

| CLK | 时钟输入 | WR信号 |

| CLR | 清零 | VCC |

| OE | 输出使能 | GND |

| CS(片选) | 片选 | 地址译码器输出 |

这种连接方式可以确保每次写操作都触发一次锁存,从而实现数据的稳定输出。

3.2 单片机端口资源分配与规划

3.2.1 并行端口P0、P2的功能划分

C51单片机的并行端口P0和P2是扩展外部设备时的关键资源。P0口通常复用为数据总线和低8位地址线,而P2口用于高8位地址线。在连接74HC273时,P0口负责数据传输,而P2口用于地址译码控制。

例如,若将74HC273映射到地址0x8000,则P2口的高地址线(如P2.0~P2.1)接入74LS138地址译码器,生成片选信号CS。P0口负责将数据发送到74HC273的数据输入端。

// 示例代码:通过P0口向74HC273写入数据

void WriteTo74HC273(unsigned char data_out) {

P2 = 0x80; // 设置高位地址

P0 = data_out; // 将数据写入P0口

WR = 0; // 拉低WR,触发CLK上升沿

WR = 1; // 恢复WR为高电平

}

代码逻辑分析:

- 第一行:设置P2口为0x80,用于选中74HC273所在的地址段;

- 第二行:将要输出的数据写入P0口;

- 第三行:将WR信号拉低,产生一个下降沿,从而触发CLK的上升沿;

- 第四行:恢复WR为高电平,完成一次写操作。

该代码实现了对74HC273的单次写入操作,适用于静态LED显示或数据锁存场景。

3.2.2 地址译码与片选信号的生成

为了实现多个外设的共存,需要通过地址译码器(如74LS138)生成唯一的片选信号。例如,将P2.0~P2.2接入74LS138的A、B、C输入端,G1接高电平,G2A、G2B接地,从而根据地址选择不同的外设。

以下为地址译码器与74HC273的连接表:

| 地址线 | 74LS138输入 | 片选输出 | 外设 |

|---|---|---|---|

| P2.0 | A | Y0 | 74HC273 |

| P2.1 | B | Y1 | 外设2 |

| P2.2 | C | Y2 | 外设3 |

当P2口为0x80(即P2.7为1,其余为0)时,P2.0~P2.2为000,对应74LS138的Y0输出低电平,选中74HC273。

3.3 接口电路的时序匹配与优化

3.3.1 单片机读写周期与芯片响应时间的匹配

74HC273的工作时序必须与C51单片机的读写周期严格匹配。C51单片机的标准读写周期约为480ns(12MHz晶振),而74HC273的建立时间(tSU)和保持时间(tH)分别为5ns和3ns,满足时序要求。

以下为典型读写周期的时序图(使用Mermaid绘制):

sequenceDiagram

participant MCU

participant 74HC273

MCU->>74HC273: 地址建立

MCU->>74HC273: WR拉低(CLK上升沿)

74HC273-->>MCU: 数据锁存

MCU->>74HC273: WR恢复高电平

图3.2 写操作时序流程图

为确保数据在CLK上升沿前已稳定,需在WR拉低前将P0口数据准备好。若系统频率较高,建议在WR操作前后加入短延时(如调用_nop_()函数)。

3.3.2 延时与同步控制策略

在高速系统中,74HC273可能因响应速度跟不上单片机而造成数据不稳定。为此,可以采用以下同步控制策略:

- 插入NOP延时 :在关键时序操作前后插入空操作,确保时序满足要求;

- 使用定时器控制写入周期 :通过定时器中断控制写入时间,提高同步精度;

- 使用硬件等待状态 :通过插入等待周期(如使用ALE信号控制)来延长写入时间。

#include <intrins.h>

void DelayNOP() {

_nop_();

_nop_();

_nop_();

_nop_();

}

void WriteTo74HC273_Sync(unsigned char data_out) {

P2 = 0x80;

P0 = data_out;

DelayNOP(); // 插入延时确保数据稳定

WR = 0;

DelayNOP();

WR = 1;

}

代码逻辑分析:

- 使用

_nop_()函数插入4个空操作指令,延时约4个机器周期; - 在数据写入P0口后插入延时,确保数据在CLK上升沿前稳定;

- WR信号操作前后均插入延时,提高同步性和稳定性。

该方法适用于对时序要求较高的场合,如高速LED刷新或并行数据采集系统。

小结

本章围绕74HC273与C51单片机之间的接口设计展开,详细介绍了硬件连接方案、端口资源分配、地址译码机制以及时序匹配与优化策略。通过合理配置数据总线、地址总线和控制信号线,并结合软件延时与同步控制,可以实现高效、稳定的数据输出接口。下一章将深入探讨如何使用C语言控制74HC273实现具体的数据输出功能,包括LED动态显示与刷新控制等内容。

4. C语言控制74HC273实现数据输出

在嵌入式系统开发中,数据的输出控制是核心任务之一。74HC273作为一款具有8位D型锁存器的TTL兼容CMOS芯片,广泛用于扩展单片机的并行输出接口。本章将围绕C51环境下使用C语言对74HC273进行数据写入与控制展开,详细介绍如何通过C语言实现对IO端口的操作、锁存控制的实现,以及LED动态显示等典型应用场景。

4.1 C51中IO端口的定义与访问

在C51单片机编程中,IO端口的访问与控制是实现外部设备通信的基础。74HC273通过单片机的并行端口(如P0、P2)连接,其控制信号(如CLK、CLR)也需要通过特定的IO引脚进行控制。因此,首先需要在C语言中正确地定义这些端口和位。

4.1.1 使用sbit与sfr定义特殊功能寄存器

在C51中, sfr (Special Function Register)用于定义特殊功能寄存器,而 sbit (Special Bit)用于定义寄存器中的特定位。通过这两个关键字,可以方便地访问和控制单片机的IO端口及控制信号。

#include <reg51.h>

sfr DATA_PORT = 0x80; // P0端口地址为0x80

sbit CLK = P2^0; // 使用P2.0作为CLK信号

sbit CLR = P2^1; // 使用P2.1作为CLR信号

代码解释:

sfr DATA_PORT = 0x80;:定义P0端口为DATA_PORT,其地址为0x80。通过该变量可以一次性访问P0的全部8位。sbit CLK = P2^0;:将P2.0引脚定义为CLK信号,用于控制74HC273的时钟输入。sbit CLR = P2^1;:将P2.1引脚定义为CLR信号,用于清零74HC273内部锁存器。

这种方式使得程序中可以直接通过变量名来操作硬件,提高代码可读性和维护性。

4.1.2 IO端口的直接访问与宏定义技巧

在实际编程中,我们经常需要对某些IO操作进行封装,以提高代码的复用性。可以通过宏定义或函数封装的方式实现。

#define SET_CLK() CLK = 1

#define CLR_CLK() CLK = 0

#define SET_CLR() CLR = 1

#define CLR_CLR() CLR = 0

void delay(unsigned int ms) {

unsigned int i, j;

for(i = 0; i < ms; i++)

for(j = 0; j < 123; j++);

}

代码解释:

#define SET_CLK() CLK = 1:定义宏函数SET_CLK(),将CLK置高。#define CLR_CLK() CLK = 0:宏函数CLR_CLK()用于将CLK拉低。delay()函数:实现一个简单的软件延时函数,用于控制信号的时序。

通过宏定义,可以简化控制信号的设置,提高代码执行效率,同时增强可读性。

4.2 数据写入与锁存控制的实现

74HC273的核心功能是通过CLK信号将数据锁存到输出端。要实现数据的写入与锁存控制,需要按照一定的时序将数据送上数据总线,并配合时钟信号完成锁存操作。

4.2.1 写入数据的C语言代码实现

以下是一个向74HC273写入数据的示例代码,演示如何将一个字节的数据通过P0端口发送,并通过CLK信号完成锁存。

void write_74hc273(unsigned char data) {

DATA_PORT = data; // 将数据写入P0口

delay(1); // 稳定数据总线

SET_CLK(); // 拉高CLK,触发锁存

delay(1);

CLR_CLK(); // 拉低CLK,完成锁存

}

代码解释:

DATA_PORT = data;:将传入的数据赋值给P0端口,即送入74HC273的数据输入端。SET_CLK();:上升沿触发74HC273的锁存动作。CLR_CLK();:下降沿完成锁存过程。

流程图说明:

graph TD

A[开始] --> B[设置数据总线]

B --> C[延时稳定数据]

C --> D[拉高CLK]

D --> E[延时]

E --> F[拉低CLK]

F --> G[锁存完成]

该流程图清晰展示了数据写入到锁存完成的全过程。

4.2.2 锁存信号的产生与时序控制

74HC273的锁存动作依赖于CLK信号的上升沿。为了确保数据被正确锁存,必须满足其建立时间(Setup Time)和保持时间(Hold Time)的要求。

建立与保持时间表:

| 参数 | 最小值 | 单位 |

|---|---|---|

| 建立时间 t_su | 20 | ns |

| 保持时间 t_h | 10 | ns |

在C51中,由于主频较低(通常为12MHz),延时函数 delay(1) 大约可以实现1ms的延时,远大于74HC273所需的ns级时序要求,因此能够保证时序的正确性。

进一步优化建议:

如果使用更高主频的单片机,应考虑使用精确的延时函数,例如:

void precise_delay(unsigned int cycles) {

while(cycles--) {

_nop_(); // 单周期空操作

}

}

这样可以更精确地控制CLK的高电平和低电平时间,避免因时序错误导致数据锁存失败。

4.3 LED动态显示与刷新控制

74HC273常用于LED数码管的驱动控制。在多位LED动态显示中,74HC273可作为段码输出锁存器,通过定时刷新实现多位显示。

4.3.1 多位LED显示的扫描原理

动态显示的基本原理是利用人眼的视觉暂留效应,快速轮询每一位LED,使它们依次点亮,从而形成连续的视觉图像。

假设使用4位共阴数码管,段码由74HC273锁存,位选由另一个IO口控制:

unsigned char code seg_code[] = {0x3F, 0x06, 0x5B, 0x4F, 0x66, 0x6D, 0x7D, 0x07, 0x7F, 0x6F}; // 0~9段码

unsigned char digit_pos[] = {0xFE, 0xFD, 0xFB, 0xF7}; // 位选信号

unsigned char display_buffer[4] = {0, 1, 2, 3}; // 显示缓冲区

参数说明:

seg_code[]:存储0~9的段码,用于控制数码管的各个段。digit_pos[]:用于控制哪一位数码管点亮。display_buffer[]:保存要显示的数字内容。

4.3.2 利用定时器与中断实现动态刷新

为了实现高效的动态显示,通常使用定时器中断来控制刷新频率。以下是一个基于定时器0的中断服务程序示例:

unsigned char current_digit = 0;

void timer0_isr(void) interrupt 1 {

TH0 = 0xFC; // 设置初值,1ms中断一次

TL0 = 0x18;

// 关闭所有数码管

P1 = 0xFF;

// 输出段码

DATA_PORT = seg_code[display_buffer[current_digit]];

// 锁存段码

SET_CLK();

delay(1);

CLR_CLK();

// 输出位选

P1 = digit_pos[current_digit];

// 更新位选索引

current_digit = (current_digit + 1) % 4;

}

void main(void) {

TMOD = 0x01; // 定时器0模式1

TH0 = 0xFC;

TL0 = 0x18;

ET0 = 1; // 使能定时器0中断

EA = 1; // 使能全局中断

TR0 = 1; // 启动定时器0

while(1); // 主循环空转

}

代码解释:

timer0_isr:定时器0中断服务程序,每1ms执行一次。DATA_PORT = seg_code[display_buffer[current_digit]];:将当前位的段码送到74HC273。SET_CLK();和CLR_CLK();:完成段码的锁存。P1 = digit_pos[current_digit];:选择当前要显示的数码管。current_digit:循环更新显示位,实现扫描显示。

动态刷新流程图:

graph TD

A[开始定时器] --> B[进入中断]

B --> C[关闭所有数码管]

C --> D[送入段码]

D --> E[锁存段码]

E --> F[输出位选]

F --> G[更新位索引]

G --> H[返回主程序]

该流程清晰地展示了中断服务程序中完成的动态刷新步骤。

通过上述内容的学习,读者可以掌握如何使用C语言控制74HC273实现数据输出、锁存控制以及LED动态显示等典型应用。下一章将深入介绍如何基于74HC273构建完整的数字输出系统,并进行调试与优化。

5. 基于74HC273的数字输出系统设计与调试

5.1 系统整体设计方案

5.1.1 功能需求与硬件模块划分

在设计基于74HC273的数字输出系统之前,首先明确系统功能需求。例如:设计一个8位LED数码管显示系统,能够动态显示00~99的数字,并支持通过按键修改显示内容。

根据功能需求,我们将整个系统划分为以下几个硬件模块:

| 模块名称 | 功能描述 |

|---|---|

| C51单片机 | 控制核心,负责处理数据与控制信号生成 |

| 74HC273芯片 | 数据锁存器,用于扩展并行输出接口 |

| LED数码管 | 显示输出内容,采用共阴极数码管 |

| 按键输入 | 用户输入接口,用于修改显示内容 |

| 振荡电路 | 提供系统时钟信号 |

| 复位电路 | 实现系统复位功能 |

5.1.2 系统软件流程图与模块化设计

系统软件采用模块化设计,主要包括以下功能模块:

- 主控模块:负责整体流程控制;

- 显示控制模块:实现LED数码管的扫描与刷新;

- 输入检测模块:检测按键输入状态;

- 数据处理模块:根据输入更新显示内容;

- 延时与定时模块:提供精确延时与定时中断支持。

以下是系统主程序流程图(使用Mermaid语法):

graph TD

A[开始] --> B[初始化系统]

B --> C[初始化IO端口与定时器]

C --> D[读取按键状态]

D --> E{是否有按键按下?}

E -->|是| F[更新显示数据]

E -->|否| G[保持原数据]

F --> H[写入74HC273锁存器]

G --> H

H --> I[启动LED扫描显示]

I --> J[进入下一轮循环]

J --> D

该流程图清晰地展示了系统运行的主流程,便于后续代码编写与调试优化。

5.2 实际电路搭建与测试

5.2.1 PCB布局与焊接注意事项

在实际搭建电路时,PCB布局应遵循以下原则:

- 电源与地线分离布线 ,减少干扰;

- 高频信号线走线短且直 ,避免形成环路;

- 去耦电容尽量靠近芯片电源引脚 ;

- 使用插拔式接口 ,便于调试与更换元件;

- 74HC273的CLK与CLR信号线应远离模拟电路部分 ,以防干扰。

焊接时注意:

- 确保74HC273与单片机之间的数据线连接正确;

- 检查电源极性,避免反接烧毁芯片;

- 使用万用表测量焊点是否短路或虚焊;

- LED数码管公共端连接是否正确(共阴或共阳)。

5.2.2 使用万用表与示波器进行信号检测

为了验证电路是否正常工作,可以使用以下工具进行检测:

万用表检测:

- 测量74HC273的VCC与GND之间电压是否为5V;

- 测量LED数码管各段引脚电压是否随数据变化;

- 检查按键按下时是否能正确拉低或拉高输入电平。

示波器检测:

- 观察CLK信号是否为方波,频率是否符合预期;

- 检查74HC273的数据输出是否与单片机发送一致;

- 分析LED刷新频率是否稳定,是否存在闪烁现象。

示例:使用示波器查看CLK信号波形如下:

___ ___ ___ ___

_| |___| |___| |___| |_ ...

5.3 系统调试与故障排查

5.3.1 常见问题分析与解决策略

在调试过程中,可能会遇到以下常见问题:

| 现象 | 可能原因 | 解决方法 |

|---|---|---|

| LED不亮 | 电源未接通或数码管极性错误 | 检查电源连接,确认数码管类型 |

| 显示混乱 | 数据线接错或段码错误 | 检查数据线连接,核对段码表 |

| 显示闪烁 | 刷新频率过低 | 增加定时器中断频率 |

| 按键无效 | 输入引脚未上拉/下拉 | 添加上拉电阻或修改IO配置 |

| 74HC273无输出 | CLK信号未触发 | 检查CLK控制代码与电路连接 |

5.3.2 性能优化与稳定性提升方法

为了提高系统稳定性和响应速度,可以进行以下优化:

- 增加延时补偿 :在数据写入后添加微秒级延时,确保74HC273正确锁存;

- 使用中断驱动方式 :将LED刷新任务交给定时器中断,避免主程序阻塞;

- 优化段码表结构 :使用数组存储段码,便于快速查表显示;

- 电源去耦优化 :在74HC273电源引脚附近添加100nF陶瓷电容;

- 使用状态机管理显示流程 :提升系统可维护性与扩展性。

示例:优化段码查表代码如下:

// 定义共阴数码管段码表(0~9)

unsigned char code seg_code[] = {0x3F, 0x06, 0x5B, 0x4F, 0x66, 0x6D, 0x7D, 0x07, 0x7F, 0x6F};

// 显示函数

void display_digit(unsigned char digit) {

P0 = seg_code[digit]; // 将段码写入P0口

delay_us(1); // 微秒延时,确保锁存

CLK = 1; // 触发CLK上升沿

CLK = 0;

}

通过上述优化措施,系统运行更加稳定,同时具备良好的可扩展性,为后续功能扩展(如添加LCD显示、蜂鸣器报警等)提供了良好的基础。

简介:本文介绍如何使用C51单片机通过74HC273芯片控制八位LED灯的输出。74HC273是一款8位透明锁存器,适用于数据存储与传输。结合C51编程环境,通过配置单片机并行接口和控制锁存使能信号,实现对LED灯的动态显示控制。文章涵盖硬件连接、程序设计、时序控制等内容,适用于51、96、88系列及ARM架构微控制器的学习与应用。

更多推荐

已为社区贡献15条内容

已为社区贡献15条内容

所有评论(0)