PCIE 中断设计

详细介绍PCI/PCIe中断设计

三种中断触发模型:

1. Legacy PCI Interrupt Delivery

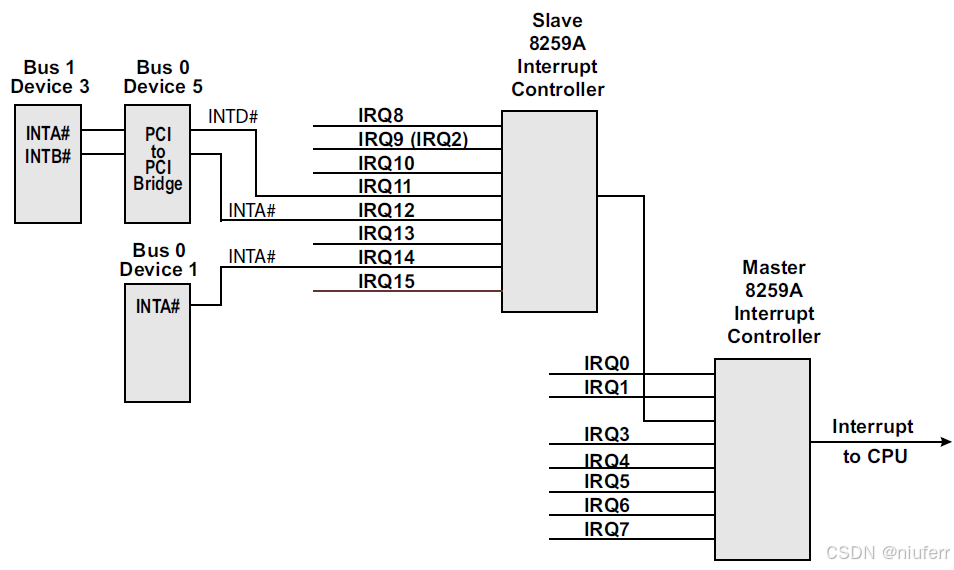

这是PCI 总线的中断方式,跟寻常理解的中断触发方式一样,通过引脚的电平信号触发。一共有四根中断线(INTA, INTB, INTC, INTD).在常规的系统中一般会将这四根中断线或在一起然后传递给中断控制器。

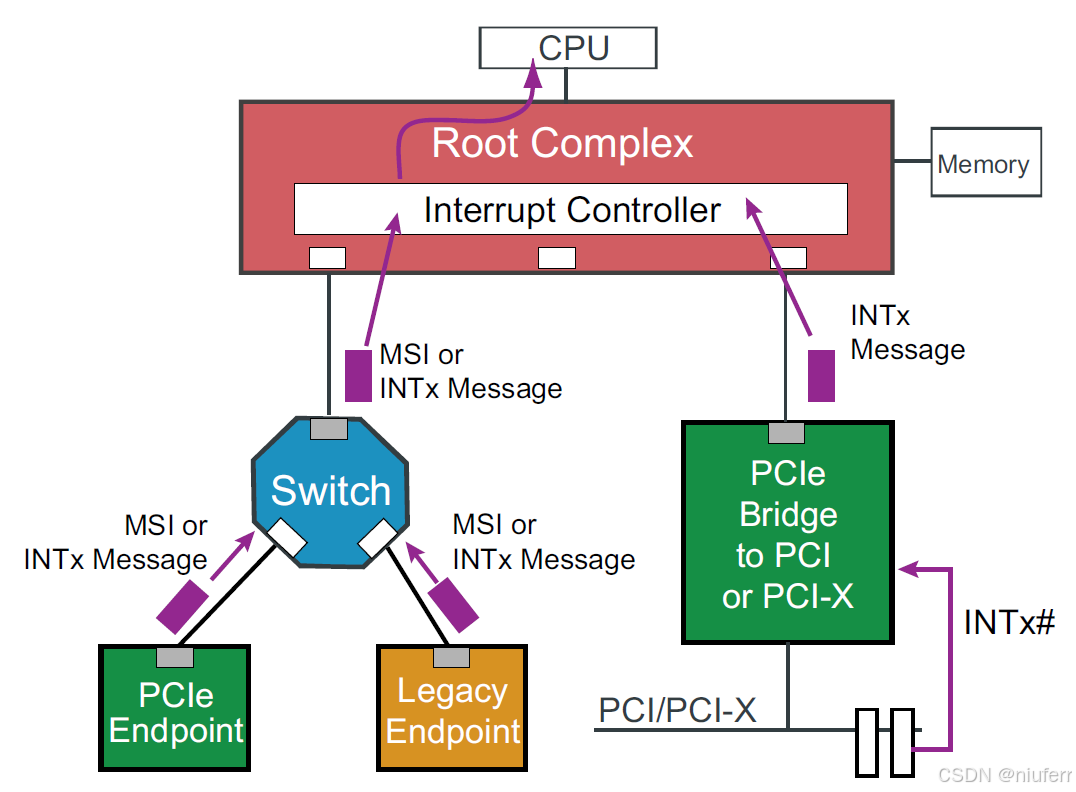

PCIe为了向下兼容,也为了减少引脚数量,也支持Legacy 中断方式,但是不再有INTA-D这样具体的硬件信号线。

主要场景如下图:

PCI/PCI-X 设备接入 PCIe Bridge,PCIe Bridge收到legacy interrupt的中断电平信号将其转成 INTx Message TLP包上发给RC,由RC将这个中断传递给中断控制器。

Legacy Interrupt 示例

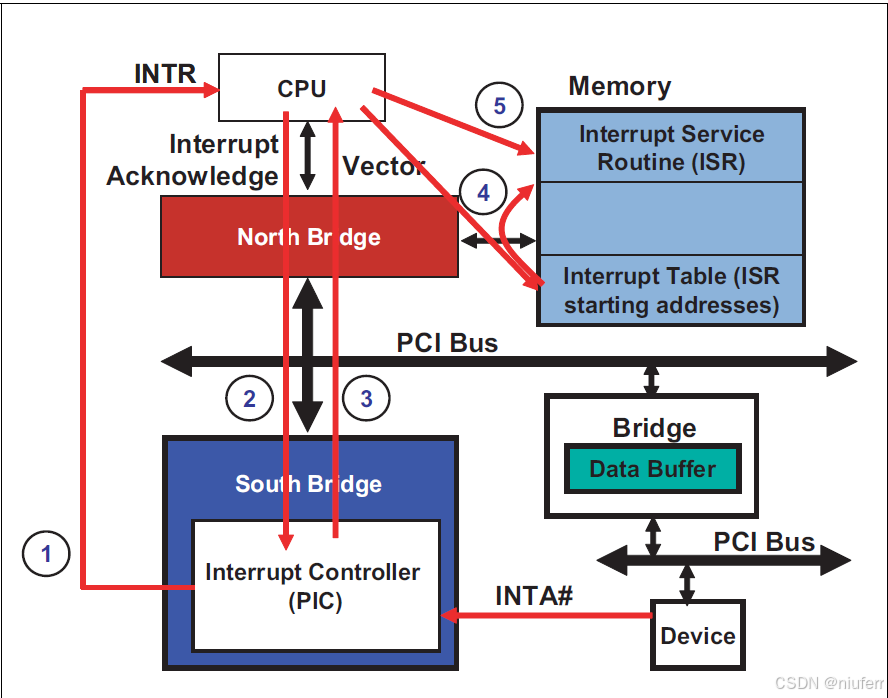

PCI Device的INT信号接到南桥中断控制芯片PIC,PIC的中断信号INTR接入CPU

- 当Device发生中断事件,INTA硬件信号拉起,此时中断控制器PIC收到中断信号并把它发送给CPU(PIC控制的中断有很多,这些中断信号一起或给cpu)。

- CPU收到了中断,需要确认是哪个中断需要处理,于是通过处理器总线发出“Interrupt Acknowledge”的特殊指令

- PIC收到这个指令,会返回8-bit的Interrupt Vector来表示目前pending的最高优先级的中断向量

- CPU通过这个Vector从Interrupt Table中找到对应的handler。

- 在handler中完成业务,并向device下发指令拉低INTA信号

SMP系统支持

上面的示例是单CPU的情况下,SMP系统场景下,每个CPU都会有各自的业务,这些业务都会依赖device中断,所以先前的单cpu模型那种一根中断线的设计无法满足需求。硬件的中断信号线只有一根,如果接给一个cpu那没有问题,如果接给多个cpu,当中断发生,每个cpu都会收到中断信号,那么无论这个中断与这个CPU是否相关,每个cpu都要发出Interrupt Acknowledge给PIC查询,这样的设计冗余且低效而且混乱。

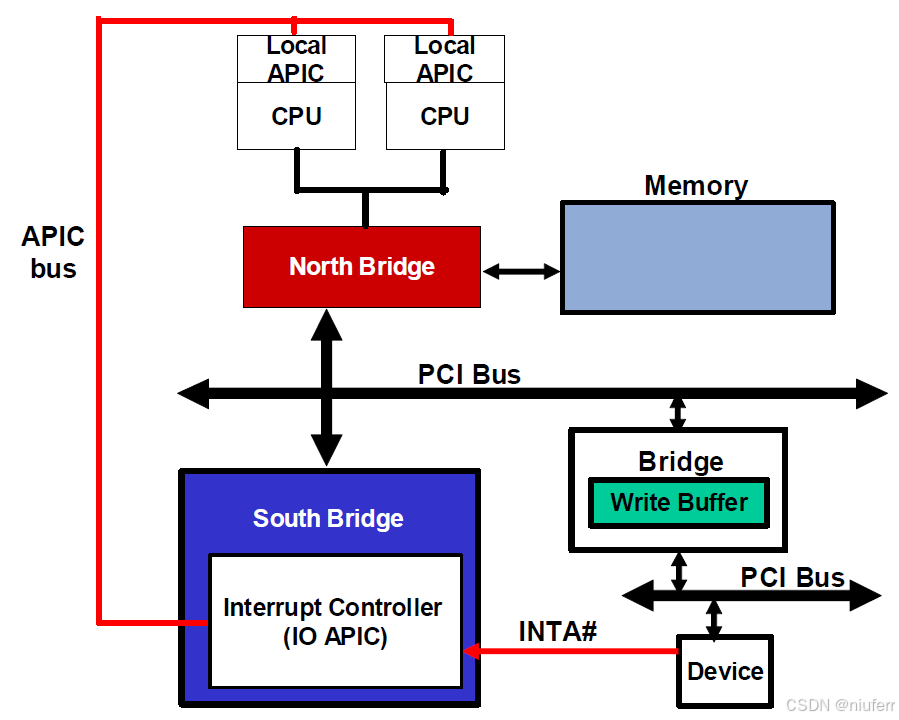

针对SMP系统推出APIC Model,有 IO-APIC(Advanced Programmable Interrupt Controller)这么个中断控制器。其中包含一个APIC bus和Logic APIC组件。

这样PIC与CPU连接的不再是硬件的中断信号,而是一个APIC bus连接在每个cpu的Logic APIC模块上,这个APIC bus上传递中断message,中断的message里包含了Interrupt Vector。

CPU在开始初始化各自的Logic APIC,静态分配中断,当中断产生,每个cpu的Logic APIC都会收到message,然后根据先前的配置,决定是否将中断报给CPU。因为先前已经配置好了,虽然每个Local APIC依然会收到这些message,但是CPU能够判断这这个中断的message是不是给自己的(甚至在Local APIC就能屏蔽掉不是给自己的中断)。

这个设计确实有了很多提升,上图中IO APIC向CPU传递中断的信号从单信号线变成了一个传递message的bus,但是对于外设(device)来说,其实它上报中断的手段并没有改变,还是中断信号线。在图上不难看出Device上报中断流程是从Device发出INTA#中断到IO APIC再走APIC bus到Local APIC再到CPU,当Device很多的时候,每个Device都会有自己的INTA#,这种结构非常冗余且造成硬件的设计灾难。那为啥不让外设直接发送中断message到 Logic APIC呢?有现成的数据通路,Device-> PCI Bus -> Bridge -> PCI BUS -> CPU。 将device的中断传递从INTA#这样的硬件信号线,变成一个pci的TLP上报给RC给CPU,这就是MSI Interrupt Delicery。

2. MSI Interrupt Delicery

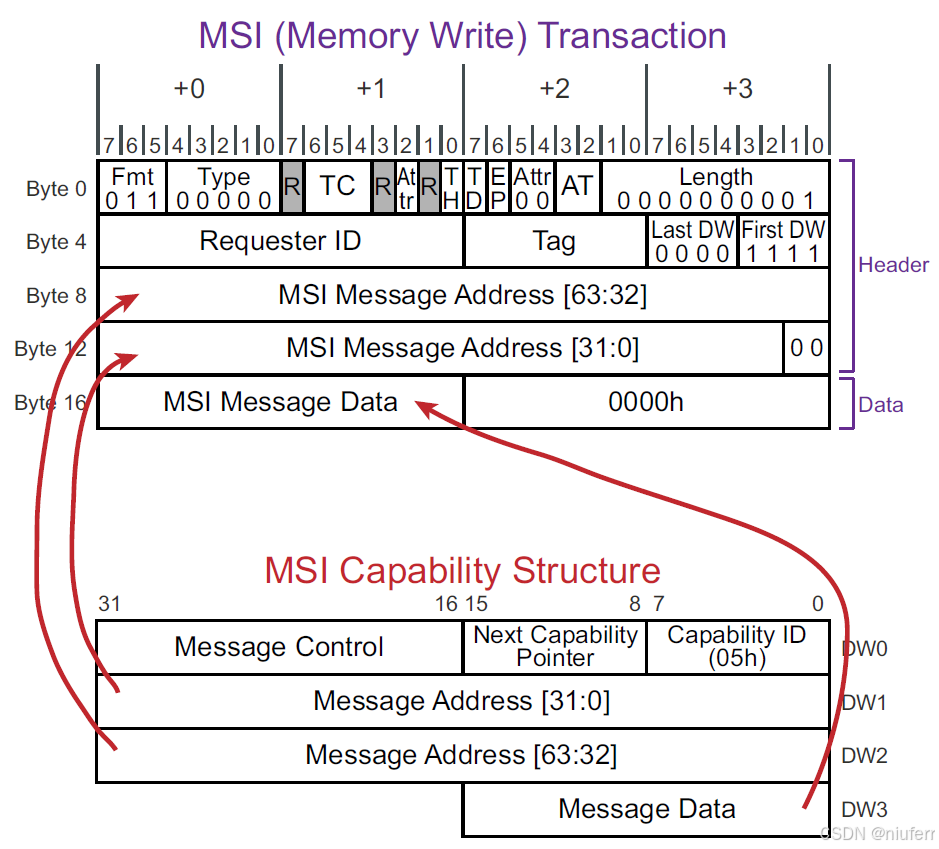

- MSI 没有硬件的中断信号pin脚,他是通过 memory write TLP包来上报中断,区别于legacy interrupt的 message TLP。

- MSI向host发送memory write TLP包来写host的memory固定地址值来触发中断,这个必须要求中断控制器支持MSI,因为只有这样中断控制器才能识别到MSI中断并发出中断信号给CPU。

- 不同的处理器对PCIe 设备发出的MSI 报文的解释并不相同。但是PCIe 设备在提交MSI中断请求时, 都是向MSI/ MSI-X Capability 结构中的Message Address 的地址写Message Data数据, 从而组成一个存储器写TLP, 向处理器提交中断请求。

- MSI 中断机制最多只能支持32 个中断请求,而且要求中断向量连续。

PCIe 设备可以使用MSI 或者MSI-X 报文向处理器提交中断请求, 但是对于某个具体的PCIe 设备, 可能仅支持一种方式。在PCIe 设备中含有两个Capability 结构, 一个是MSI Capability结构, 另一个是MSI-X Capability 结构。通常情况下一个PCIe 设备仅包含一种结构,或者为MSI Capability 结构, 或者为MSI-X Capability 结构。

MSI Capability 结构

MSI的Capability结构在 PCI-compatible config space的前256字节。

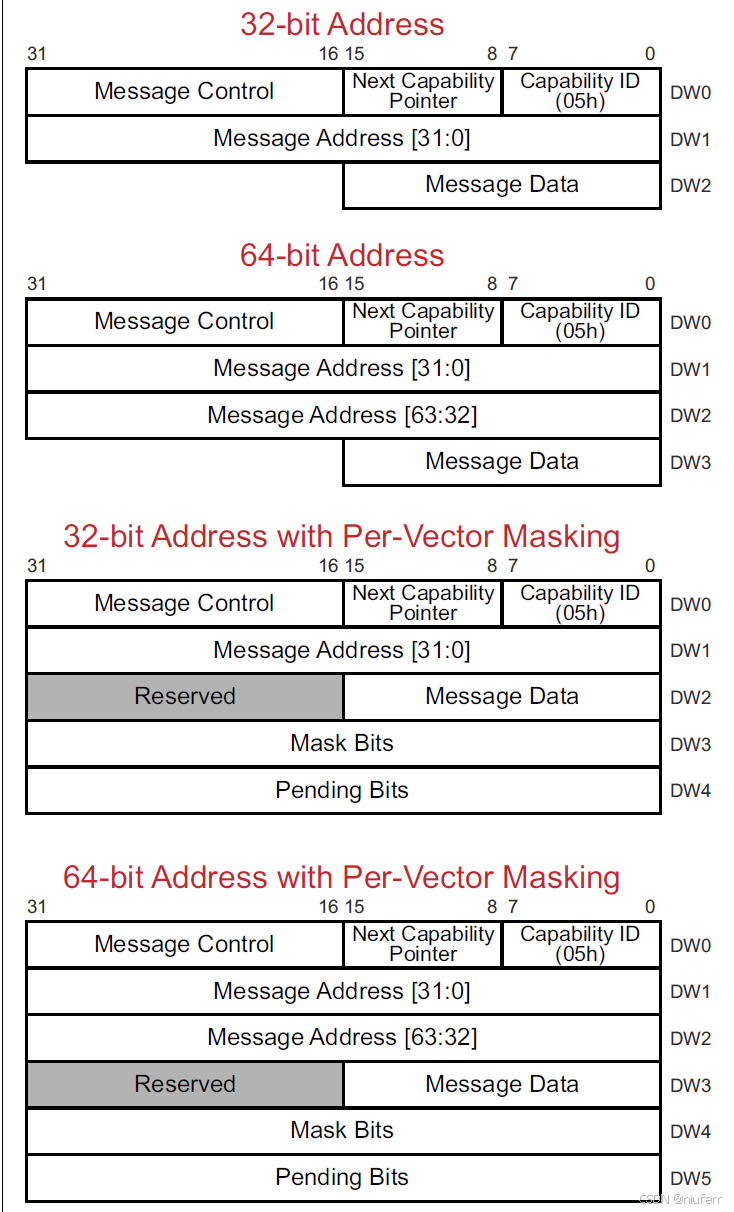

根据32/63bit以及是否支持mask,一共分四种类型的capability 结构。

Capability ID: 0x05, Read-Only

Next Capability Pointer:指向下一个Capability,Read-Only,如果是0则表示到达Capability list的末尾。

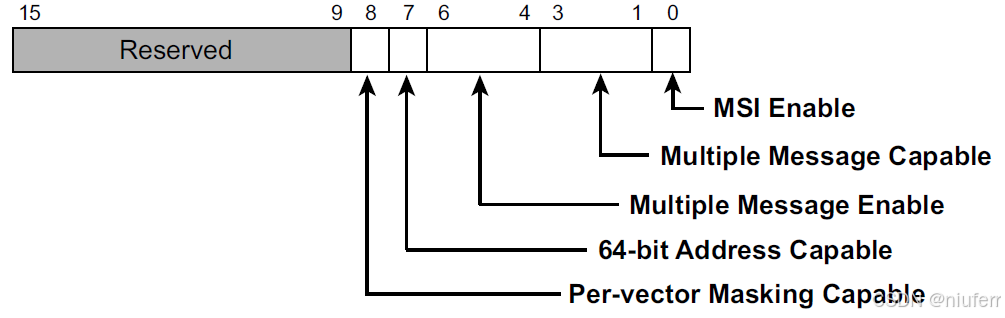

Message Control Register

控制寄存器:

|

Bits |

Name |

attr |

Description |

|

0 |

MSI Enable |

RO |

0: MSI disable 1: MSI enable |

|

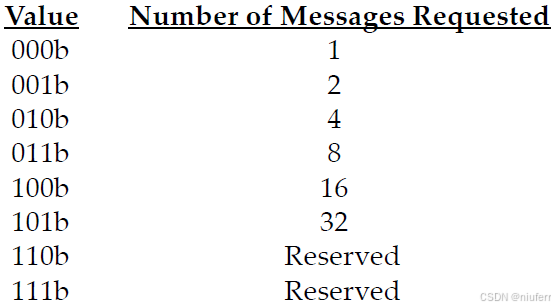

3:1 |

Multiple Message Capable |

RO |

Host读这个寄存器来获取需要支持多少个中断

|

|

6:4 |

Multiple Message Enable |

R/W |

Host先读上面的 Multiple Message Capable寄存器获取需要支持多少中断,然后进行中断申请,资源分配等,最终将分配到的中断资源回写进这个寄存器。也决定了pcie device能够修改的Message Data 字段的最低位数目。

|

|

7 |

64-bit Address Capable |

RO |

0:32bit地址 1:64bit地址 |

|

8 |

Per-vector Masking Capable |

RO |

0:没有实现mask和pending机制,软件无法屏蔽单独的中断 1:实现了mask和pending机制,每个中断可以被软件单独屏蔽 |

Message Address Register:

Host分配的一个地址,在这个地址写值会触发中断。32/64 bits由Message Control Register的bit7决定。

Message Data register:

Host负责初始化的值,其最低的几位表示中断vector,具体是几位由Multiple Message Enable 寄存器的值来决定。

当MSI中断产生,device会通过memory write tlp向Message Address Register地址写Message Data register的值,然后Message Data register低地址几bit的值就表征了中断号也叫interrupt vector。MSI中断要求中断向量连续的要求也就来自这里,MSI最多支持32个中断,Message Data register低位bit也是连续的,对于有的中断控制器来说这就要求中断号连续。

Mask Bits Register and Pending Bits Register:

跟普通的中断控制器的mask和pending作用一样,mask用以屏蔽单个中断,pending表示中断是否已经发生。

差异就是,当mask为1时,如果有中断,那么对应的pending应该置一,如果mask为0,表示不屏蔽中断,pcie设备

发出中断时会将pending清零。

当发出MSI中断时的tlp header:

3. MSI-X Model

MSI-X引入的原因,或者说MSI-X的引入解决了MSI的哪些不足

- MSI 32个中断向量不足以支持某些应用的问题

- 唯一的Message Address Register地址使得跨多个cpu的静态中断分发变得困难,每个中断向量有独立的Message Address Register提高灵活性

- MSI连续的中断向量不容易区分中断优先级,而且有些系统有足够的中断号但却不一定能够分配出足够的连续的中断号

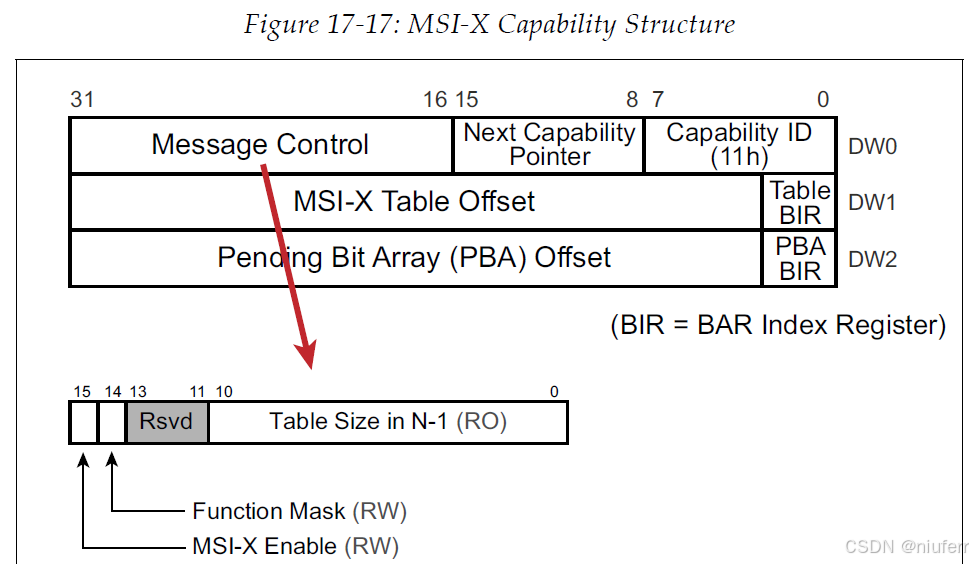

MSI-X Capability Structure

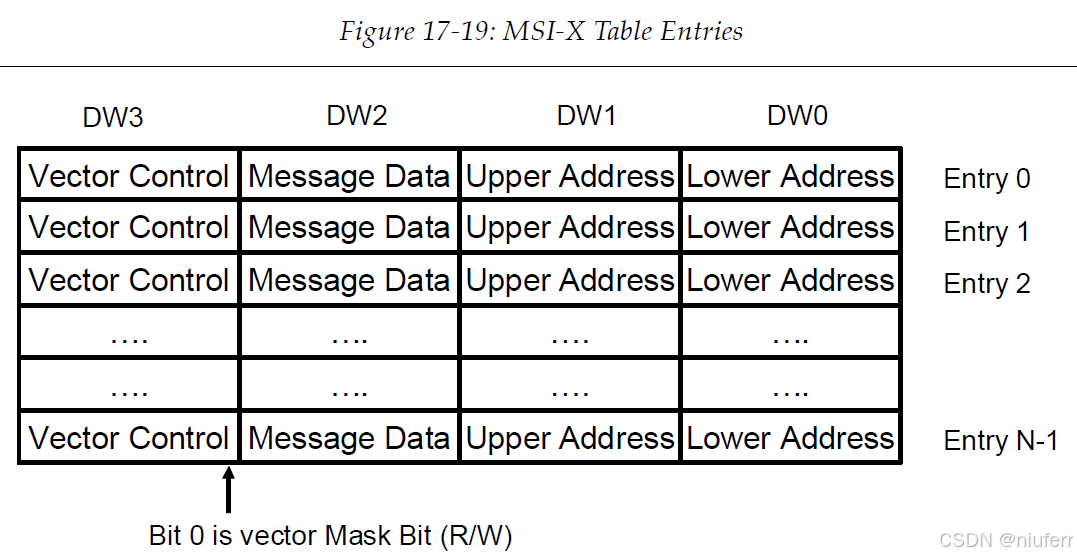

MSI-X给每个中断向量都分配了独立的Message Address Register和Message Data register。这些内容组成了一个表存放在device的BAR空间中。(config space肯定放不下的)

|

Field name |

attr |

Description |

|

Table Size |

RO |

表示有多少中断vector |

|

Function Mask |

R/W |

中断总开关,Host软件可以通过set这个bit来屏蔽所有中断。如果这个bit为0,也可以通过mask bit来屏蔽单个中断 |

|

MSI-X Enable |

R/W |

MSI-X功能是否使能 |

●Table BIR (BAR Indicator Register)。该字段存放MSI-X Table 所在的位置, PCIe 总线

规范规定MSI-X Table 存放在设备的BAR 空间中。该字段表示设备使用BAR0~5 寄存

器中的哪个空间存放MSI-X Table。该字段由三位组成, 其中0b000~0b101 与BAR0~

5 空间一一对应。

● Table Offset 字段。该字段存放MSI-X Table 在相应BAR 空间中的偏移。

● PBA (Pending Bit Array) BIR 字段。该字段表示ssPending Table 存放在PCIe 设备的哪

个BAR 空间中, 0 表示BAR0 空间, 1 表示BAR1 空间, 依此类推。在通常情况下,

Pending Table 和MSI-X Table 存放在PCIe 设备的同一个BAR 空间中。

● PBA Offset 字段。该字段存放Pending Table 在相应BAR 空间中的偏移。

● Msg Addr。当MSI-X Enable 位有效时, 该字段存放MSI-X 存储器写事务的目的地址的低32 位。该双字的31∶2 字段有效, 系统软件可读写; 1∶0 字段复位时为0, PCIe 设备可以根据需要将这个字段设为只读, 或者可读写。不同的处理器填入该寄存器的数

据并不相同。

● Msg Upper Addr, 该字段可读写, 存放MSI-X 存储器写事务的目的地址的高32 位。

● Msg Data, 该字段可读写, 存放MSI-X 报文使用的数据。其定义与处理器系统使用的中断控制器和PCIe 设备相关。

● Vector Control, 该字段可读写。该字段只有第0 位(即Per Vector Mask 位) 有效, 其他位保留。当该位为1 时, PCIe 设备不能使用该Entry 提交中断请求,如果此时中断产生,则对应的pending位被置位,等到mask被置成0,则中断再被提交,同时pending清零; 为0 时可以提交中断请求。该位在复位时为0。Per Vector Mask 位的使用方法与MSI 机制的Mask

位类似。

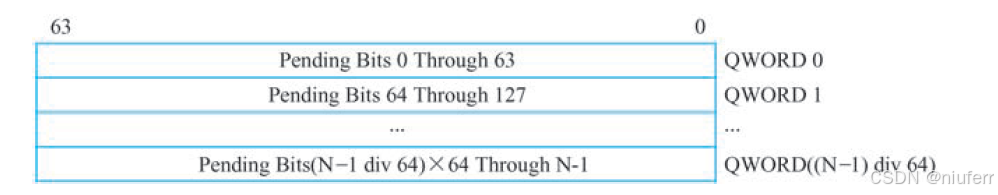

Pending Table:

Pending Table一项(64bit)对应MSI-X Table 64个entry。

cc《MindShare_PCI Express Technology 3.0.pdf》

cc《PCI Express 体系结构导读 第2版.pdf》

这两本书如果有需要,直接私信邮箱,看到会直接发邮箱。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)