数字电子电路总结

模拟电路主要是处理连续变化的模拟信号(比如电压、电流的连续波动),而数字电路是处理离散的数字信号(仅用高/低电平表示0和1),模拟信号是大自然当中本身就存在的,而数字信号却是人为进行定义的,那么如何处理数字信号以及定义数字信号呢?这就需要进行进制编码。

第一章:数字与编码

模拟电路主要是处理连续变化的模拟信号(比如电压、电流的连续波动),而数字电路是处理离散的数字信号(仅用高/低电平表示0和1),模拟信号是大自然当中本身就存在的,而数字信号却是人为进行定义的,那么如何处理数字信号以及定义数字信号呢?这就需要进行进制编码。

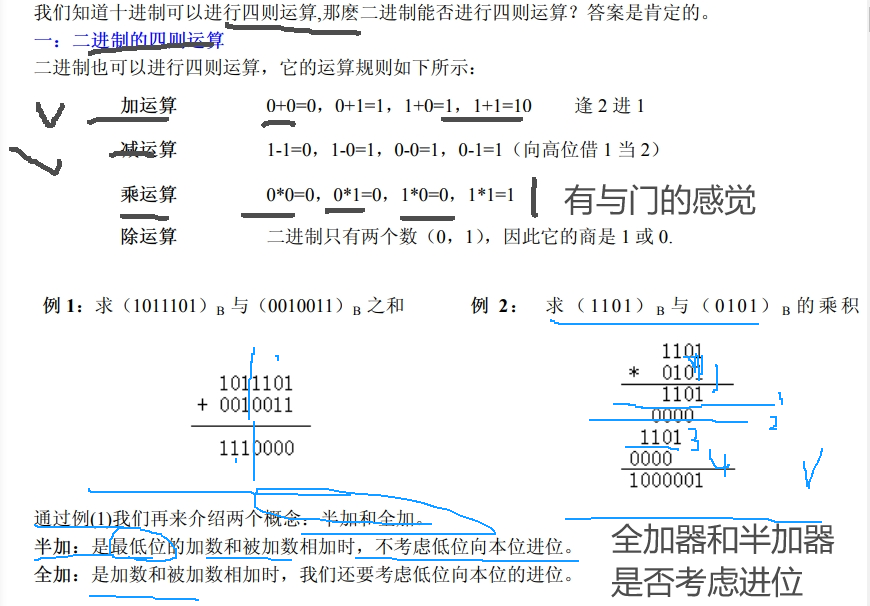

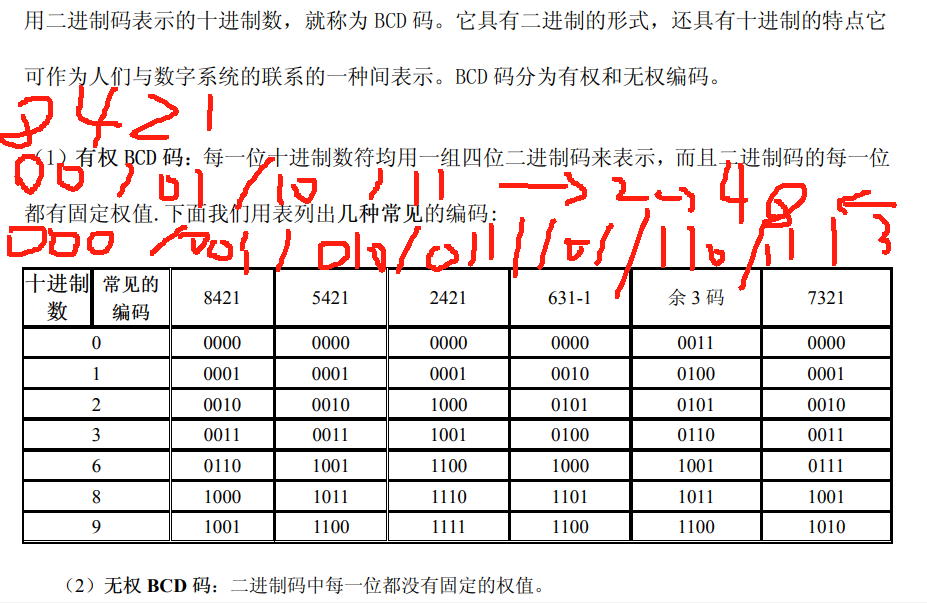

0~9这是日常生活当中使用的十进制,当数值超过了9,就需要进位1,也就变成了10;而在计算机系统里面,由于只有(通电和断电)两种状态,因此将通电(1)定义为高电平和断电(0)定义为低电平,这就是“正逻辑”里面的二进制;同时早期的计算机字长为8位、12位或者16位,1Byte = 8bit,所以可以将八进制(基数8 = 2^3)按照二进制分为三位分组,十六进制分为四位分组。

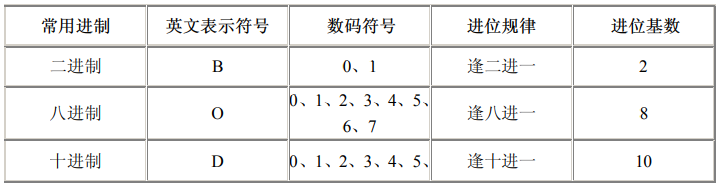

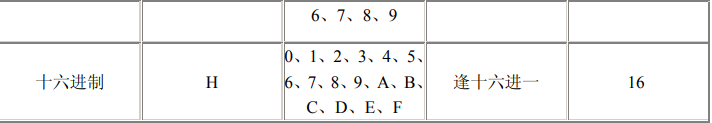

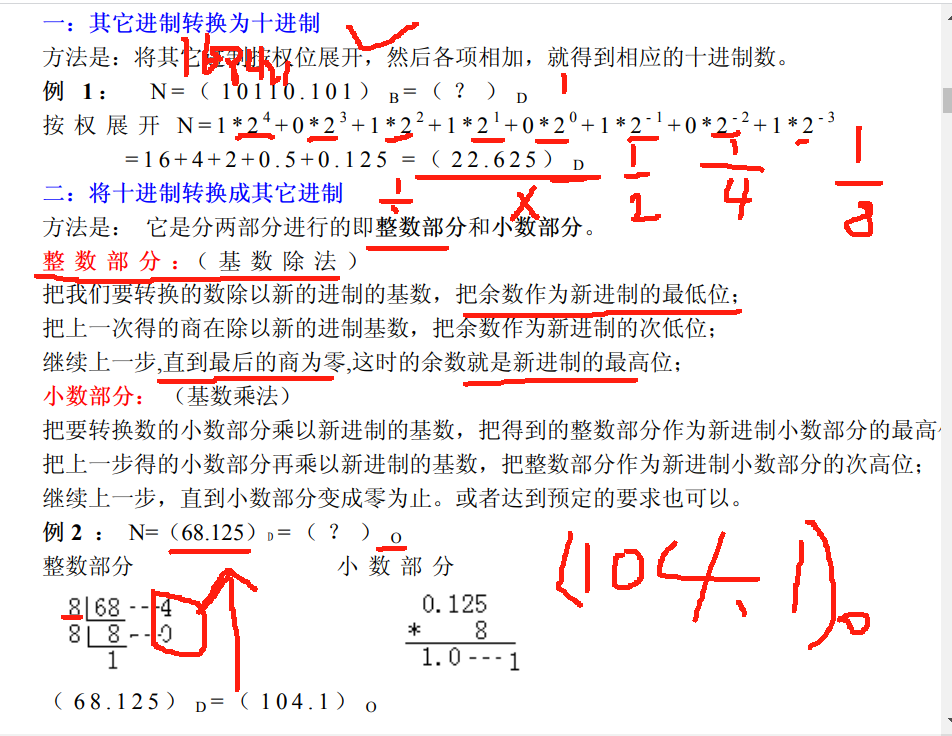

进制转换

(十进制和其他进制进行转换,其他进制和十进进行转换,二进制和八进制、十六进制转换)

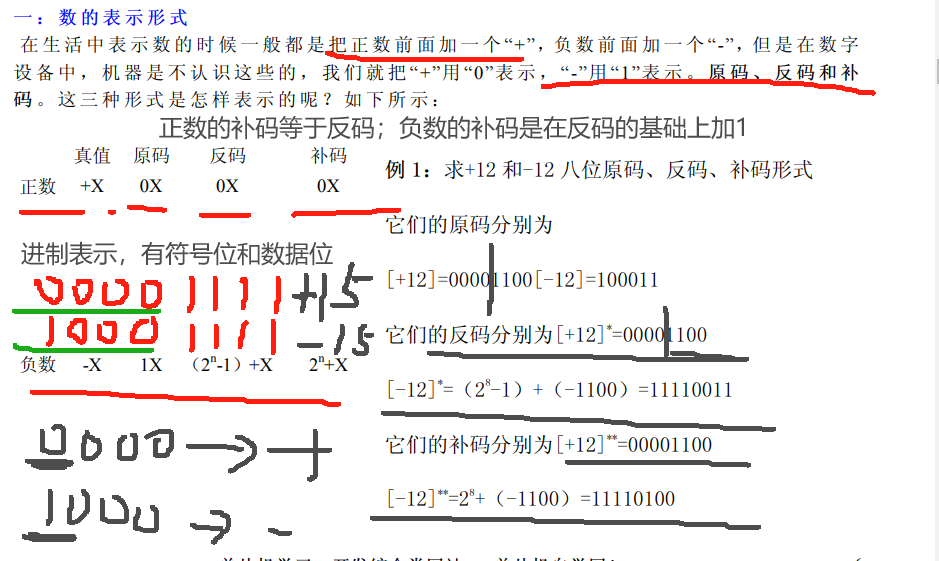

一、原码、反码、补码:计算机如何表示正负

计算机中,数值以二进制补码为基础存储和运算,这是为了简化加减运算逻辑。以下是三种编码方式的对比(以 8 位二进制为例):

1. 原码:符号位 + 数值位

- 规则:

- 最高位(第 8 位)为符号位:

0表示正数,1表示负数。 - 剩余 7 位为数值位,直接表示绝对值的二进制。

- 最高位(第 8 位)为符号位:

- 示例:

- +0:

0000 0000 - -0:

1000 0000(注意:原码中 + 0 和 - 0 是不同编码) - +5:

0000 0101 - -5:

1000 0101

- +0:

- 问题:

原码直接参与加减运算会出错(如1 + (-1)用原码计算为00000001 + 10000001 = 10000010,即-2,显然错误)。

2. 反码:原码符号位不变,数值位取反

- 规则:

- 正数反码与原码相同。

- 负数反码为原码符号位不变,数值位逐位取反(

0变1,1变0)。

- 示例:

- +5:

0000 0101(与原码相同) - -5:

1111 1010(原码1000 0101的数值位取反)

- +5:

- 问题:

虽然解决了部分加减问题,但仍存在 “+0” 和 “-0” 两种编码(00000000和11111111),浪费存储空间。

3. 补码:反码 + 1,计算机的实际存储方式

- 规则:

- 正数补码与原码、反码相同。

- 负数补码为反码加 1(即 “符号位不变,数值位取反加 1”)。

- 示例:

- +5:

0000 0101(与原码相同) - -5:

- 原码:

1000 0101 - 反码:

1111 1010 - 补码:

1111 1011(反码 + 1)

- 原码:

- +5:

- 关键特性:

- 消除 + 0/-0 歧义:补码中

0只有一种编码0000 0000,1000 0000被定义为 **-128**(8 位补码的最小值)。 - 简化运算:减法可转化为补码加法,如

1 - 1 = 1 + (-1)的补码运算为:00000001 + 11111111 = 100000000(舍弃最高位进位,结果为00000000,即正确值 0)。

- 消除 + 0/-0 歧义:补码中

二、不同进制中的正负表示

进制(如八进制、十六进制)只是二进制的人类可读性表示形式,计算机内部始终用补码存储。正负的本质是二进制编码,与进制无关:

- 八进制:负数用前缀

-表示,如-5的 8 位补码为03777773(八进制),对应二进制1111 1101。 - 十六进制:负数用前缀

-或0x后接补码,如-5的 8 位补码为0xFB(十六进制),对应二进制1111 1011。

三、总结:计算机负数表示的核心逻辑

- 符号位仅决定正负:最高位

0为正,1为负,但数值部分需按编码规则计算(原码 / 反码 / 补码)。 - 补码是核心:现代计算机几乎全用补码存储整数,通过 “取反加 1” 实现负数编码,消除 0 的歧义并简化运算。

- 进制是表象:八 / 十六进制中的负数是二进制补码的转换结果,本质仍是二进制运算。

1. 格雷码(Gray Code)(这个后面经常用)

- 性质:相邻编码仅有一个比特位不同,属于可靠性编码,主要用于减少信号变化时的误判(如编码器、数字逻辑电路)。

- 应用:数字电路状态转换、模拟 - 数字转换(ADC)中的误差抑制。

2. 曼彻斯特编码(Manchester Encoding)(后面边沿触发会接触)

- 特点:每个比特周期内包含一次电平跳变,既传输数据又携带时钟信号,可通过跳变规律检测传输错误。

- 应用:以太网物理层、低速串行通信(如 USB 1.1)

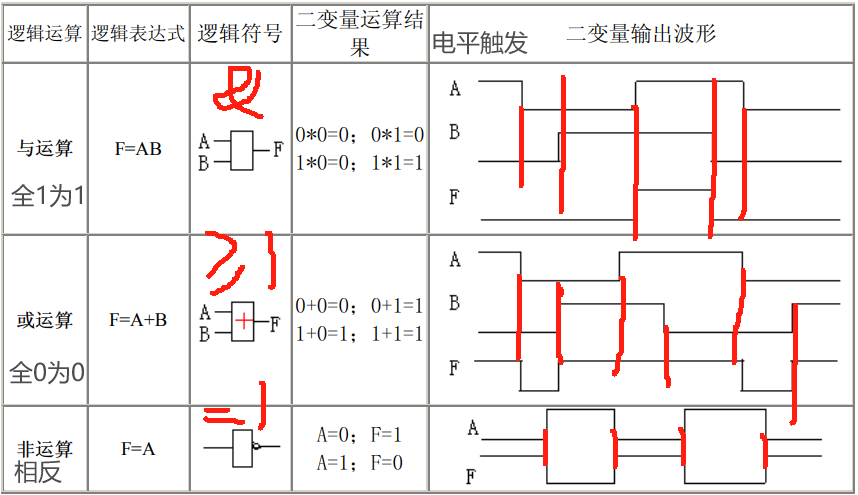

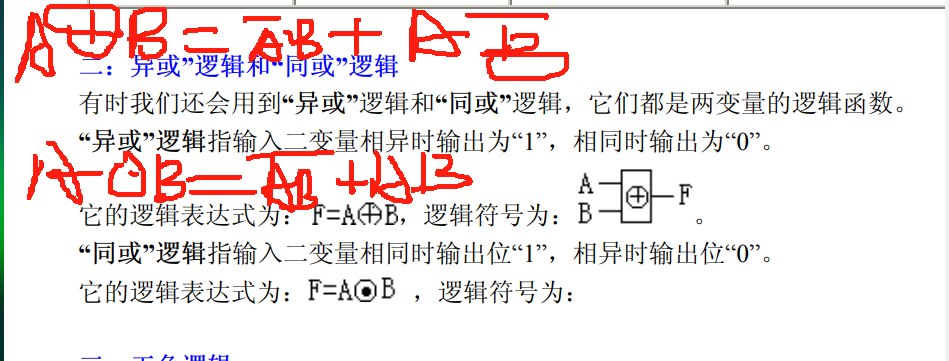

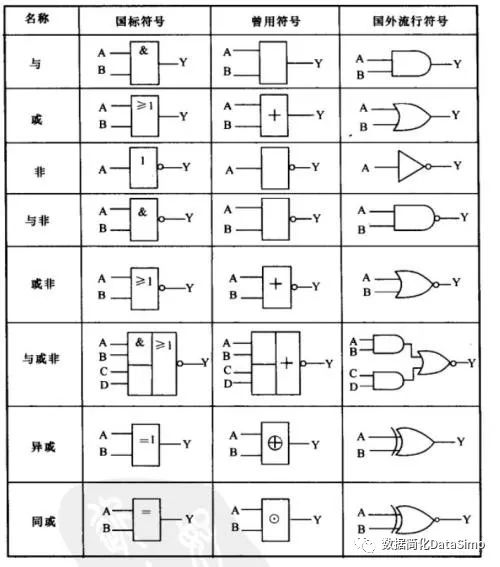

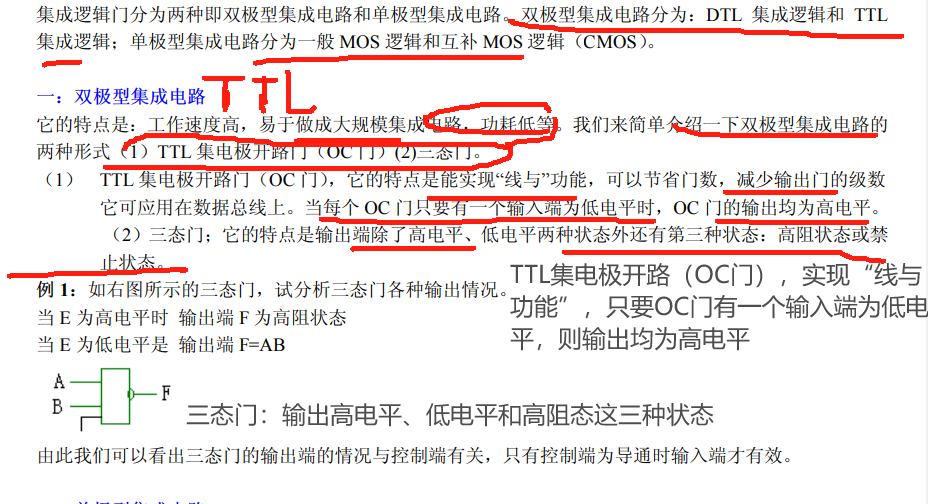

第二章:逻辑运算与逻辑门

OC 门和 OD 门的输出特性可概括为:

输入低电平时,输出端依靠外接上拉电阻才能稳定输出高电平;若无上拉电阻,输出悬空,电平不确定,并非低电平。

输入高电平时,输出端直接接地,无论是否有上拉电阻,均输出低电平(此时上拉电阻被短路,无拉高作用)。

一、OC 门(TTL 集电极开路门,Open Collector Gate)

1. 结构与原理(类比 “开关电路”)

-

TTL 门电路:传统的 TTL 门(如与非门)输出级是两个三极管(一个 NPN 上拉,一个 PNP 下拉,也就是推挽输出),能直接输出高电平(接电源)或低电平(接地),不需要外接电阻。

-

OC 门的 “特殊之处”:

OC 门的输出级 去掉了上拉三极管,只剩下一个 NPN 三极管的集电极(Collector)悬空(开路),相当于输出端是一个 “悬空的开关”,只能控制接地(低电平),无法主动输出高电平。

类比:就像你家里的灯开关,传统开关能同时控制接电源(开,高电平)和接地(关,低电平);而 OC 门的开关只能接地(关灯,低电平),接电源的线(高电平)需要你自己接一根电线到电源(即外接上拉电阻)。

2. 为什么 “输入低电平,输出高电平”?

-

当 OC 门的 输入为低电平 时:

输出端的三极管 截止(相当于开关断开),此时输出端没有接地,而是通过外接的上拉电阻连接到电源,所以输出被 “拉高” 为高电平(电源电压,如 5V)。 -

当 输入为高电平 时:

三极管 导通(相当于开关闭合),输出端直接接地,输出低电平(0V)。

关键点:OC 门自己不能输出高电平,必须靠外接的上拉电阻从电源 “拉” 高电平,这就是为什么需要上拉电阻!

3. 应用场景

-

电平转换:比如 TTL 电路(5V)要驱动 3.3V 的电路,通过调整上拉电阻的电源电压即可。

-

“线与” 功能:多个 OC 门的输出端可以并联,共享一个上拉电阻,只要有一个 OC 门输出低电平,整体输出就是低电平(相当于多个开关并联接地,只要有一个开关闭合,整体接地)。

二、OD 门(CMOS 漏极开路门,Open Drain Gate)

1. 结构与原理(类比 “MOS 管开关”)

-

CMOS 门电路:传统 CMOS 门输出级是一对互补的 MOS 管(PMOS 上拉,NMOS 下拉),能直接输出高 / 低电平。

-

OD 门的 “特殊之处”:

OD 门的输出级 去掉了 PMOS 上拉管,只剩下 NMOS 管的漏极(Drain)悬空(开路),相当于输出端只能控制接地(低电平),无法主动输出高电平(和 OC 门原理类似,但属于 CMOS 家族,用 MOS 管而非三极管)。

类比:像一个只能关灯(接地)的 MOS 管开关,开灯(高电平)需要你自己接一根线到电源(外接上拉电阻)。

2. 为什么 “输出默认是低电平,需要上拉电阻拉高”?

-

当 OD 门 不接上拉电阻时:

如果 NMOS 管截止(开关断开),输出端悬空。在 CMOS 电路中,悬空的电平是不确定的(可能飘移),但实际中如果没有上拉,可能被干扰成低电平或高电平,不安全。 -

当 接上拉电阻后:

-

若 NMOS 管截止(输入低电平),输出通过上拉电阻接电源,输出高电平;

-

若 NMOS 管导通(输入高电平),输出接地,输出低电平。

你的困惑点解答:OD 门不是 “输出都是低电平”,而是 “不接上拉电阻时无法确定电平”,必须接上拉电阻才能正常输出高电平,默认状态(截止时)靠上拉电阻拉高。

-

3. OC 门 vs OD 门

-

相同点:都需要外接上拉电阻才能输出高电平,都能实现 “线与” 功能。

-

不同点:

-

OC 门属于 TTL 电路,用三极管,电源通常是 5V;

-

OD 门属于 CMOS 电路,用 MOS 管,电源电压灵活(可接 3.3V、5V 等),功耗更低。

-

三、三态门(三态缓冲器,Tri-State Gate)

1. 三个状态:高电平、低电平、高阻态(重点!)

-

高电平(1):正常输出高电平,相当于接通电源;

-

低电平(0):正常输出低电平,相当于接地;

-

高阻态(Z):相当于输出端 完全断开(既不接电源也不接地),就像把输出端 “悬空”,对外电路没有影响。

类比:想象一个开关有三个档位:-

开(高电平,接电源)、关(低电平,接地)、悬空(高阻态,开关断开,不接任何东西)。

-

2. 工作原理

-

三态门比普通门多一个 使能信号(Enable,EN):

-

当 EN=1(使能有效) 时,三态门正常工作,输出高或低电平;

-

当 EN=0(使能无效) 时,输出端的上拉和下拉电路都断开,进入高阻态,相当于 “断开连接”。

关键点:高阻态时,三态门就像从电路中 “消失” 了,其他设备可以自由使用这条信号线。

-

3. 为什么需要高阻态?—— 解决总线冲突!

-

总线(Bus)场景:比如计算机的数据线,多个设备(如 CPU、内存、硬盘)需要共享同一根线。如果每个设备的输出都是普通门,当两个设备同时输出不同电平时,会导致短路(比如一个输出高电平,一个输出低电平,电源和地直接相连)。

-

三态门的作用:每次只有一个设备的使能信号有效(输出高 / 低电平),其他设备处于高阻态(相当于断开),这样就不会冲突了,实现 “分时复用”。

类比:就像一群人轮流用麦克风讲话,没轮到的人把麦克风关掉(高阻态),避免声音混杂。

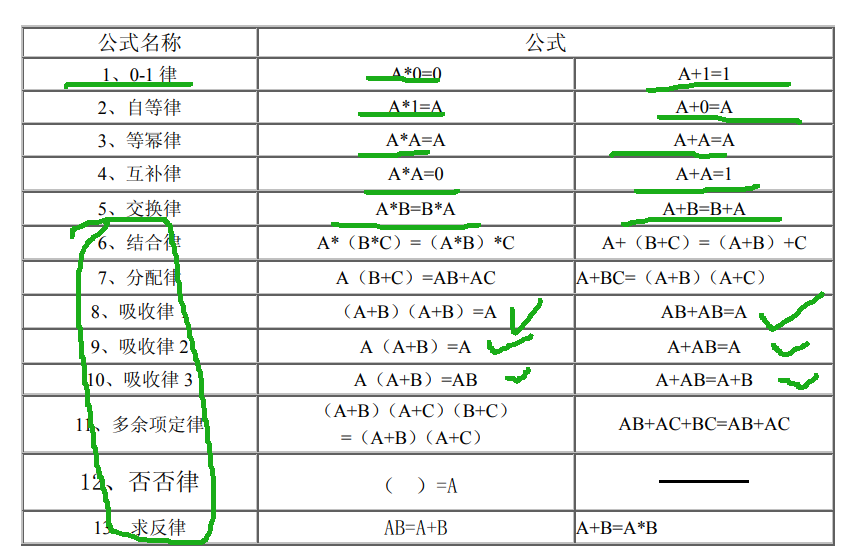

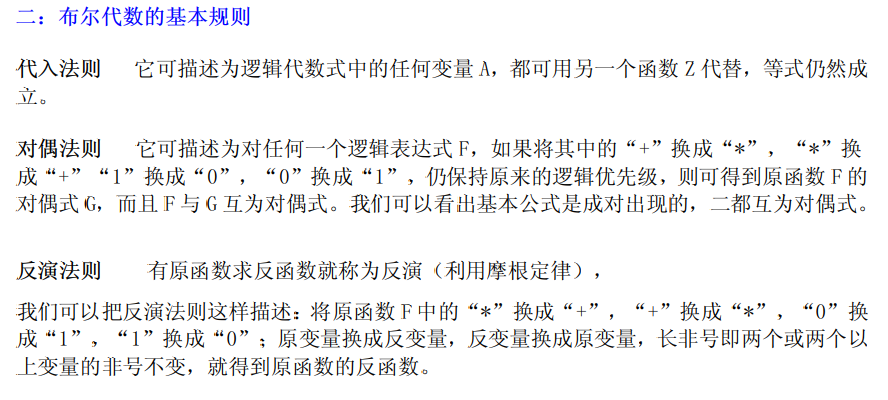

第三章:布尔代数(0/1)与逻辑函数化简

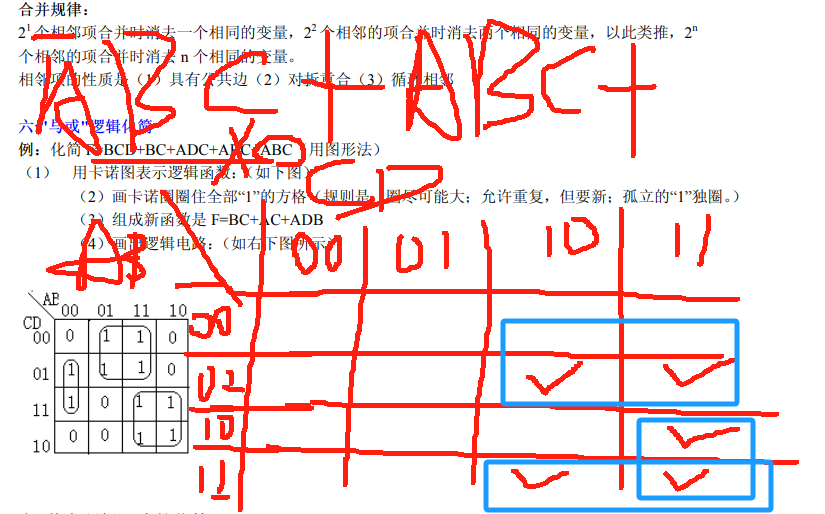

布尔代数其实就是“真”和“假”进行区分;同时逻辑函数化简的方法有两种,一个是代数法(记忆公式),化简成最简式后写出真值表,或者由真值表写出代数表达式;还有一种就是卡诺图化简法,需要学习最小项的概念!

一、最小项

对于有 n 个变量的逻辑函数,最小项是一种特殊的乘积项,每个变量都以原变量(如 A)或反变量(如 Aˉ)的形式出现且仅出现一次。例如:

- 两变量 A、B 的最小项有 AˉBˉ、AˉB、ABˉ、AB,共 22=4 个。

- 三变量 A、B、C 的最小项有 23=8 个,如 AˉBˉCˉ、AˉBˉC 等。

为方便表示,最小项常用 mi 编号,下标 i 是最小项对应二进制数的十进制值。以三变量为例:

| 编号 mi | 最小项 | 对应二进制(A,B,C) |

|---|---|---|

| m0 | AˉBˉCˉ | 000 |

| m1 | AˉBˉC | 001 |

| m2 | AˉBCˉ | 010 |

| m3 | AˉBC | 011 |

| m4 | ABˉCˉ | 100 |

| m5 | ABˉC | 101 |

| m6 | ABCˉ | 110 |

| m7 | ABC | 111 |

这就是最小项的表,它穷举了所有变量组合的最小项,是卡诺图化简的基础。

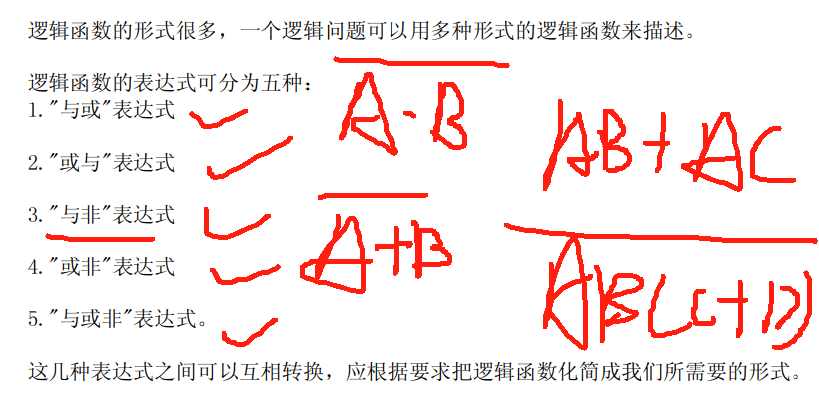

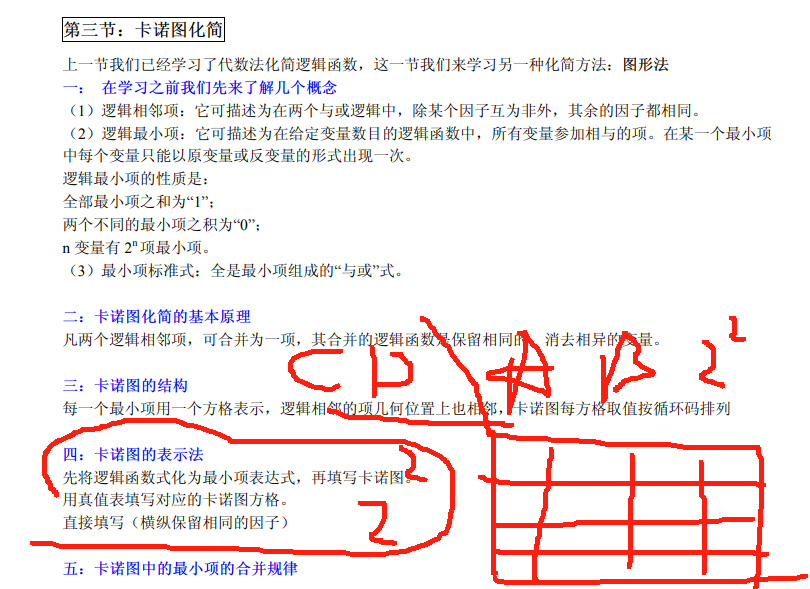

二、卡诺图

卡诺图是一种方格阵列图,每个方格代表一个最小项,方格数为 2n(n 为变量数)。其特点如下:

-

变量排列:不按二进制顺序,而是按循环码(格雷码)排列,确保相邻方格只有一个变量不同。例如,三变量卡诺图的行或列按 00,01,11,10 排列,这样 00 和 01 相邻(仅 B 从 0 变 1),01 和 11 相邻(仅 A 从 0 变 1)等。

-

逻辑相邻:几何位置相邻的方格,逻辑上也相邻(只有一个变量互补)。例如,m1(AˉBˉC) 和 m3(AˉBC) 相邻,可合并消去 B,得到 AˉC。

三、卡诺图化简

卡诺图化简逻辑函数的核心是合并相邻最小项,消去互补变量,使表达式最简。步骤如下:

-

表示逻辑函数:将逻辑函数转换为最小项表达式,在卡诺图对应方格填 1,其余填 0。

-

画卡诺圈:

-

圈住填 1 的方格,圈的大小必须是 2m(m 为整数,如 2,4,8 个方格),因为这样才能消去 m 个变量。

-

圈要尽可能大(消去变量多)、尽可能少(减少项数),且每个圈至少包含一个未被圈过的 1。

-

-

写出最简式:每个圈对应一个乘积项,圈内不变的变量保留(原变量或反变量看取值),变化的变量消去。最后将所有圈的乘积项相加。

示例:化简 F=∑m(1,3,5,7)(三变量)。

-

卡诺图中 m1(AˉBˉC)、m3(AˉBC)、m5(ABˉC)、m7(ABC) 填 1。

-

圈这四个方格,发现无论 A、B 如何变化,C 始终为 1(不变),A、B 都有 0 和 1(变化),消去 A、B,得到 F=C。

四、总结

-

最小项:逻辑函数的 “基本单元”,每个变量以原 / 反形式出现一次。

-

最小项的表:穷举所有最小项及其编号,方便在卡诺图中定位。

-

卡诺图:用方格表示最小项,通过相邻方格合并简化逻辑函数。

-

卡诺图化简:利用相邻最小项合并消去变量,圈的大小为 2m,最终得到最简逻辑表达式。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)