数字电子技术基础(五十一)——竞争与冒险

本文主要讲的是竞争和冒险,文中内容包括竞争和貌相的现象及其成因,检查竞争和冒险的方法,2线-4线译码器的竞争冒险现象以及对于竞争和冒险的消除。

目录

1 竞争与冒险

1.1 竞争和冒险的现象及其成因

由于逻辑门的传输延迟时间,电路的输出端的负载电容以及传输线的分布电容效应等因素的影响,使得传送到门电路书输入端的一组信号,到达的时间有前后之分,导致了竞争和冒险的产生。

竞争和冒险的定义:当电路输入信号改变状态时,在数字电路的输出端产生虚假信号(过渡干扰信号)的现象。

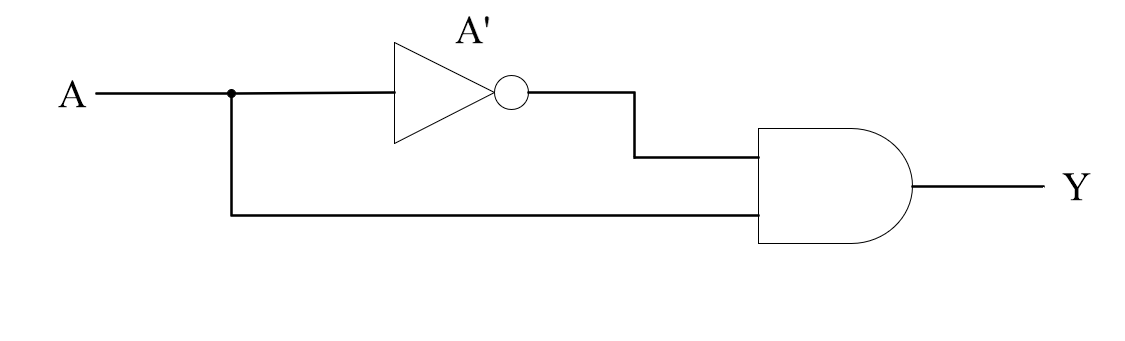

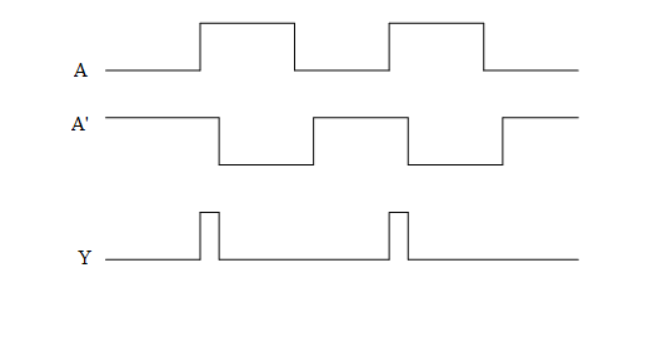

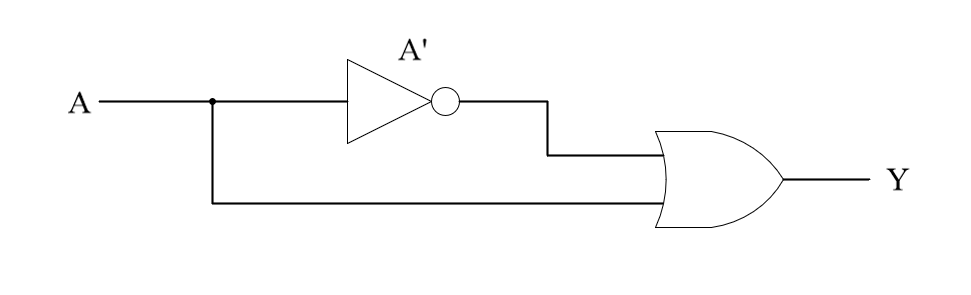

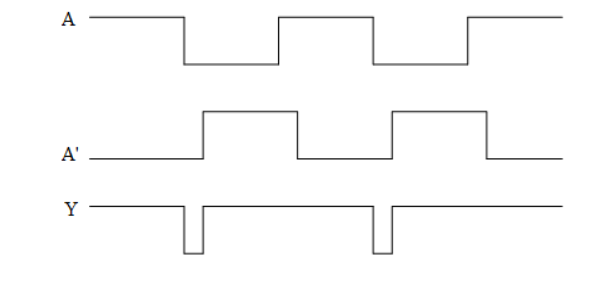

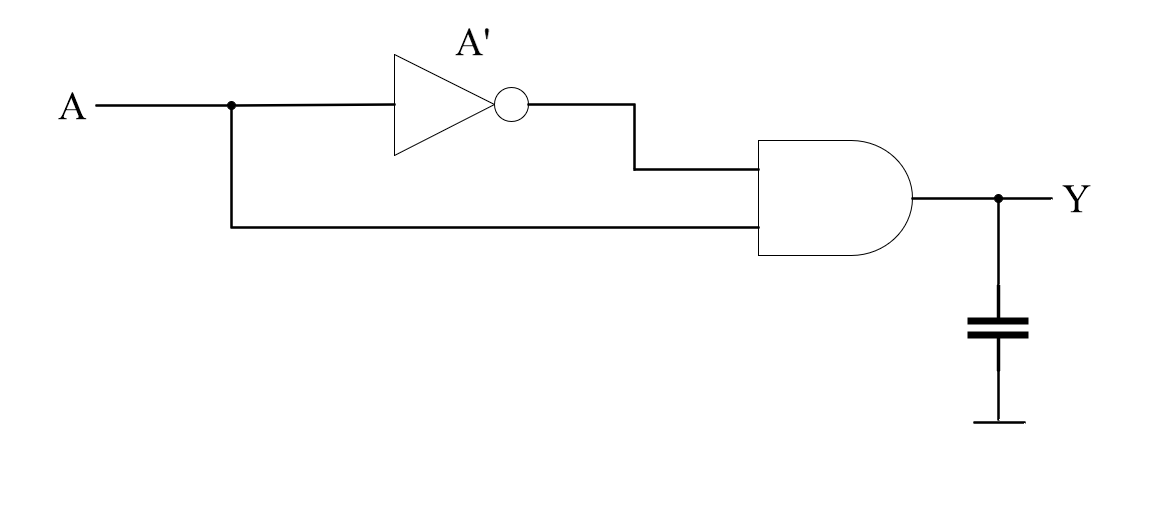

例如下面这个电路:

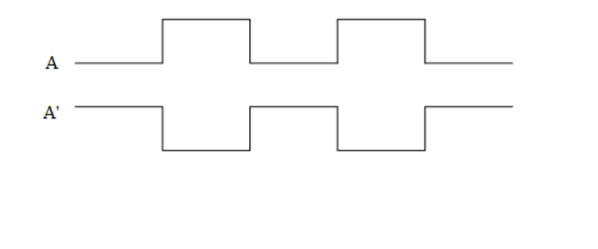

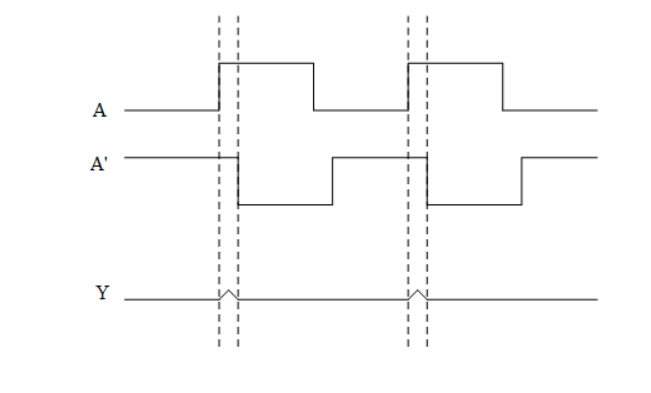

该电路的逻辑式为Y=A.A’,显然会发生“竞争-冒险”情况。理想情况下该电路的波形图如下所示:

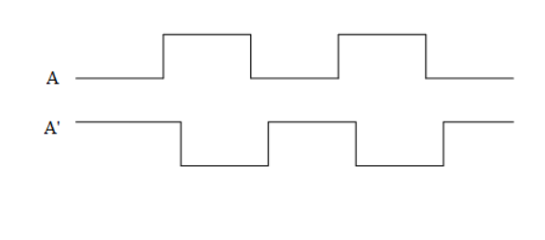

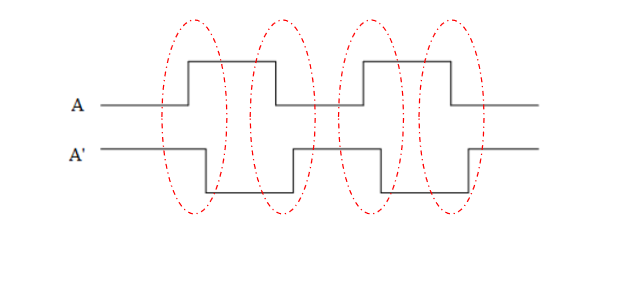

但是由于传输延迟时间的该电路的波形图可能为:

可以看到A'电平的变化明显是慢于A的:

对应Y的波形图为:

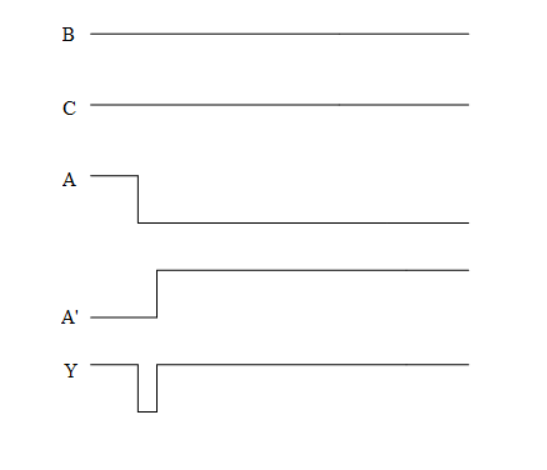

再例如这个电路图:

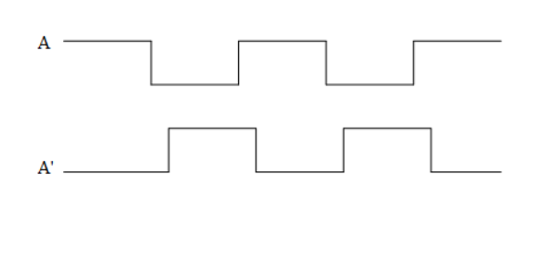

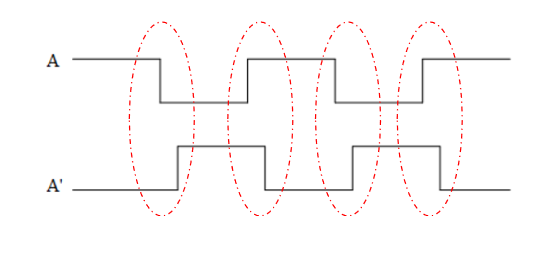

由于传输延迟时间的该电路的波形图可能为:

可以看到A'电平的变化明显是慢于A的:

对应Y的电路图为:

在某个电路的瞬间,同一个电路的输入端出现两个输入信号,同时向相反的逻辑电平体跳变的现象,这个现象称为“竞争”。

一般存在竞争现象可能在电路输出端存在干扰脉冲信号。

1.2 检查竞争和冒险的方法

(1)分析法

分析法即为判断逻辑式中是否同时为某个变量的原变量和反变量的形式。

例如对于下面这个式子:

当B=0时:

此时组合逻辑电路中,稳定时电路输出为“1”。当输入信号变化(A先变为A',A'后变化为A),但由于信号传输延迟不同,输出可能短暂出现“0。

例如对于下面这个式子:

当B=1时:

此时组合逻辑电路中,稳定时电路输出为“0”。当输入信号变化(A先变为A',A'后变化为A),但由于信号传输延迟不同,输出可能短暂出现“0。

可以总结,在一定的输入条件下,逻辑式是否转换为原变量与反变量相与或者相或的运算关系——原变量和反变量之间可能在某个门电路的输入端相遇产生竞争。

(2)观测法

通过仿真或验证实际电路进行检测。

1.3 2线-4线译码器的的竞争冒险现象

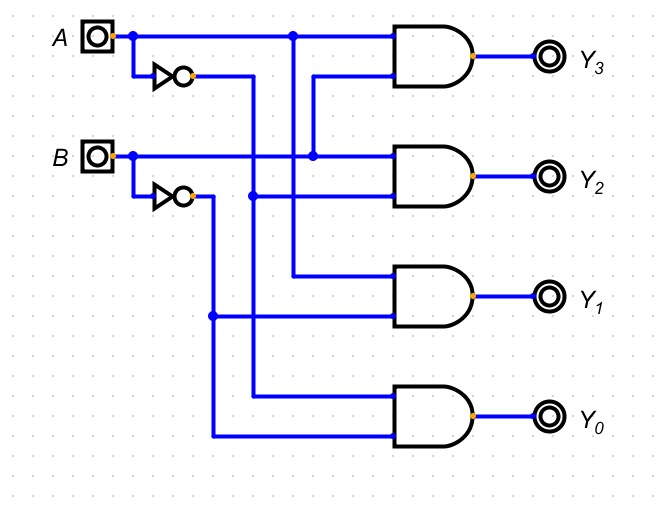

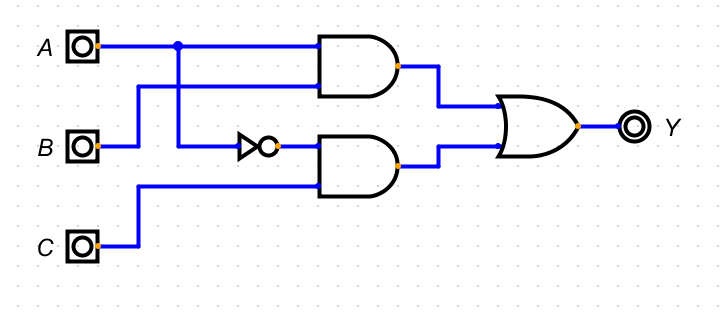

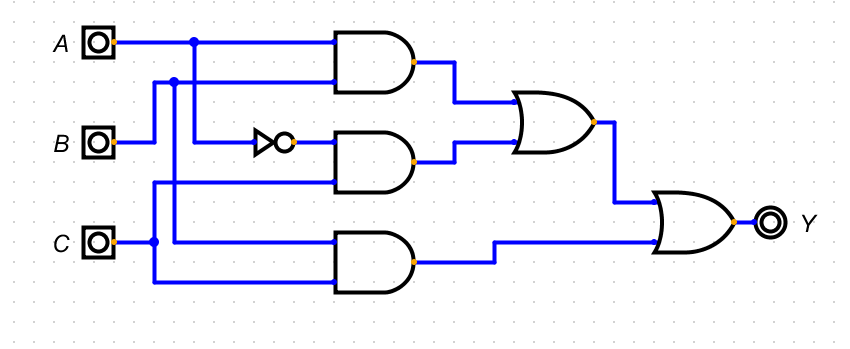

例如下面这个2线-4线译码器的电路如下所示:

其电压波形图如下所示:

(图片参考清华大学王红的《数字电子技术基础》(第六版))

在A、B的稳定状态下输出和

都应为0状态。然后由于门

和

的传输延迟时间不同,在AB从10跳变为01的过程中,

端有尖端脉冲产生,此外,由于A、B在变化过程中到达

的时刻不同,

端也有尖峰脉冲出现。

1.4 竞争和冒险的消除

(1)代数法消除竞争和冒险

保证逻辑关系不变的关系的前提下,添加冗余项。

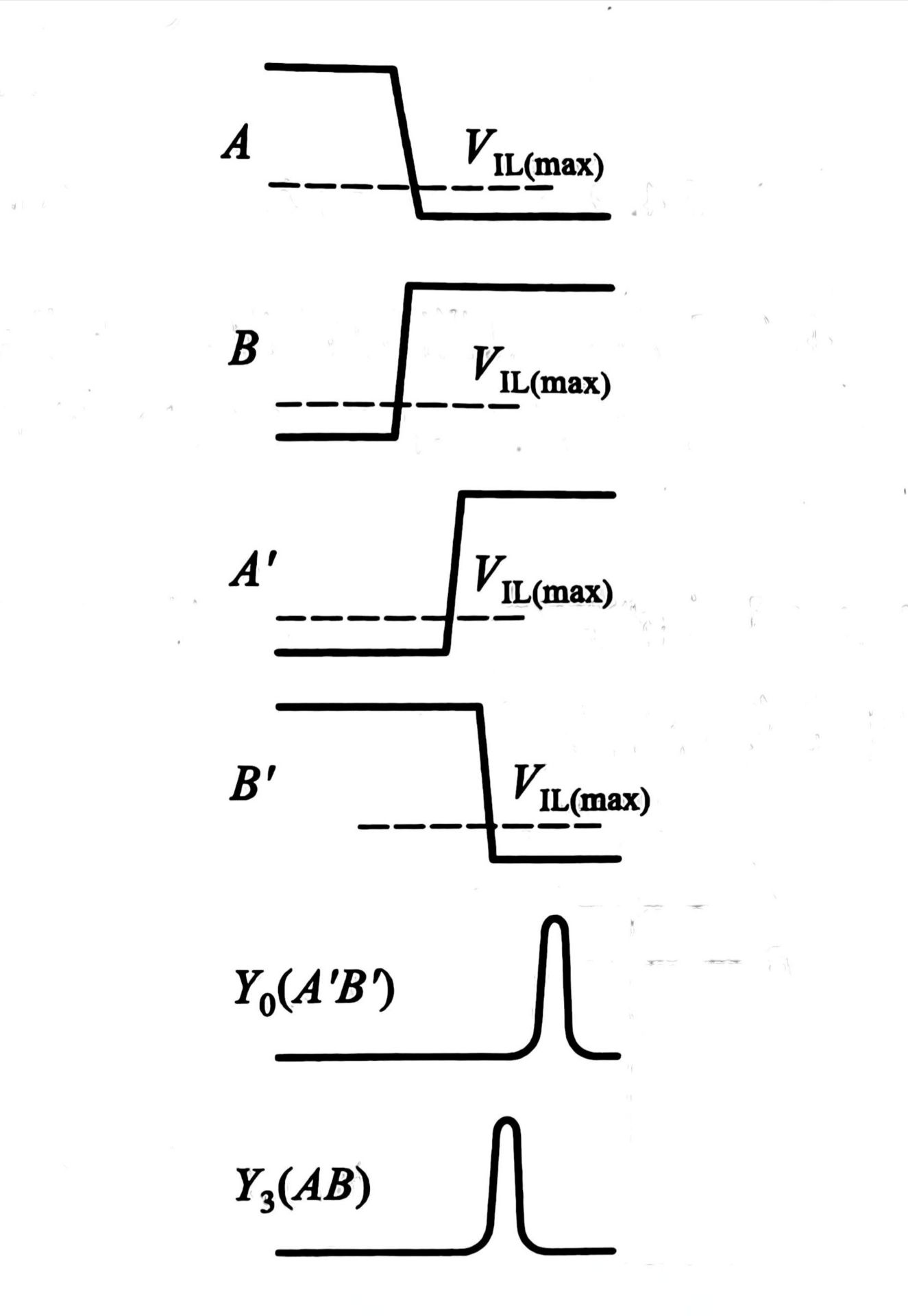

例如,对于下面这个式子:

当B=C=1,此时:

此时电路存在电路竞争-冒险现象。

当B=C=1时,如果A和A'通过变化电平,如果同时将A由高电平变为低电平,将A'由低电平变为高电平,但是由于不同的传输延迟时间,可能会出现如下所示的结果:

可以看到在上面的波形图中,输出变量Y在有段时间由高电平变为低电平,出现“竞争-冒险”现象。

此时想要消除这种可以在式子后面添加冗余项:

在上式中BC即为冗余项,当B=C=1时,此时P=A+A'+1,结果仍为1,此时消除了电路中的“竞争-冒险”现象。

对应的电路变换如下所示:

变化结果如下所示:

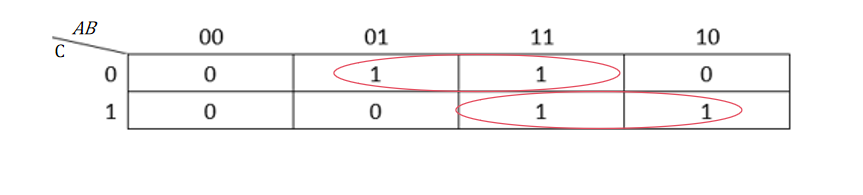

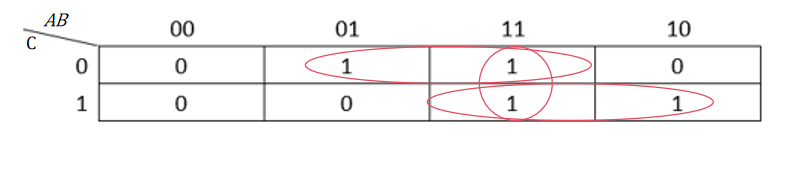

同时我们也可以通过电路得出相关的卡诺图:

通过经验可以得到,当卡诺图中两个圆相切的时候,此时可以判定该电路可能会产生冒险。而消除的方法就是将相切的两个项相互圈起来。

我们知道,AB+A'C=AB+A'C+BC是逻辑函数的常用公式,而反推的过程即为添加冗余项,这种方式可以消去“竞争-冒险”现象。

(2)加入吸收电容器

在出现冒险的部位与地之间添加电容,吸收尖峰脉冲。如下所示:

接入电容之后,波形图可能如下所示:

这种方式需要慎重选择,因为电容器的存在,使得电气时间常数变大,从而影响门电路的开关速度。

(3)引入选通脉冲

选取选通脉冲p,在电路达到稳定之后,当p的高电平出现在电路到达稳定状态之后,p的高电平稳定期的输出信号不会尖峰。当输入信号改变时,等到输出信号在一定时间稳定之监测输出信号的状态。

更多推荐

已为社区贡献39条内容

已为社区贡献39条内容

所有评论(0)