动手实践!仅用1N4148二极管、2N2222三极管和电阻,我亲手搭建了一个能工作的D型触发器!

#数字电路 #硬件DIY #触发器 #晶体管 #电子基础 #1N4148 #2N2222

大家好!我是“硬件小菜鸟”。最近在学习数字电路基础,对触发器的内部工作原理特别着迷。虽然现在一个74HC74芯片就能轻松实现D触发器功能,但总感觉用现成的IC少了点“灵魂”。为了更深入地理解其底层逻辑,我萌生了一个想法:能不能只用最基础的分立元件——二极管、三极管和电阻——来搭建一个真正能工作的D型触发器呢?

目标明确:使用手头最常见的 1N4148 开关二极管、2N2222 NPN三极管以及一些碳膜电阻,构建一个电平触发(或主从结构)的D型触发器,并且要让它能稳定地存储一位数据!

挑战与选型

-

为什么是1N4148和2N2222? 因为它们实在太常见、太基础了!1N4148开关速度快,正向压降典型,非常适合数字逻辑中的“与门”构建。2N2222则是经典的通用小功率NPN管,开关特性良好,成本低廉,是做反相器和缓冲器的理想选择。

-

核心难点: 用分立元件实现D触发器,本质上需要构建两个互联的SR锁存器(或类似结构),并通过时钟信号控制数据的采样和传输。时序控制、门电路的搭建、信号的隔离都是挑战。

我的电路设计思路

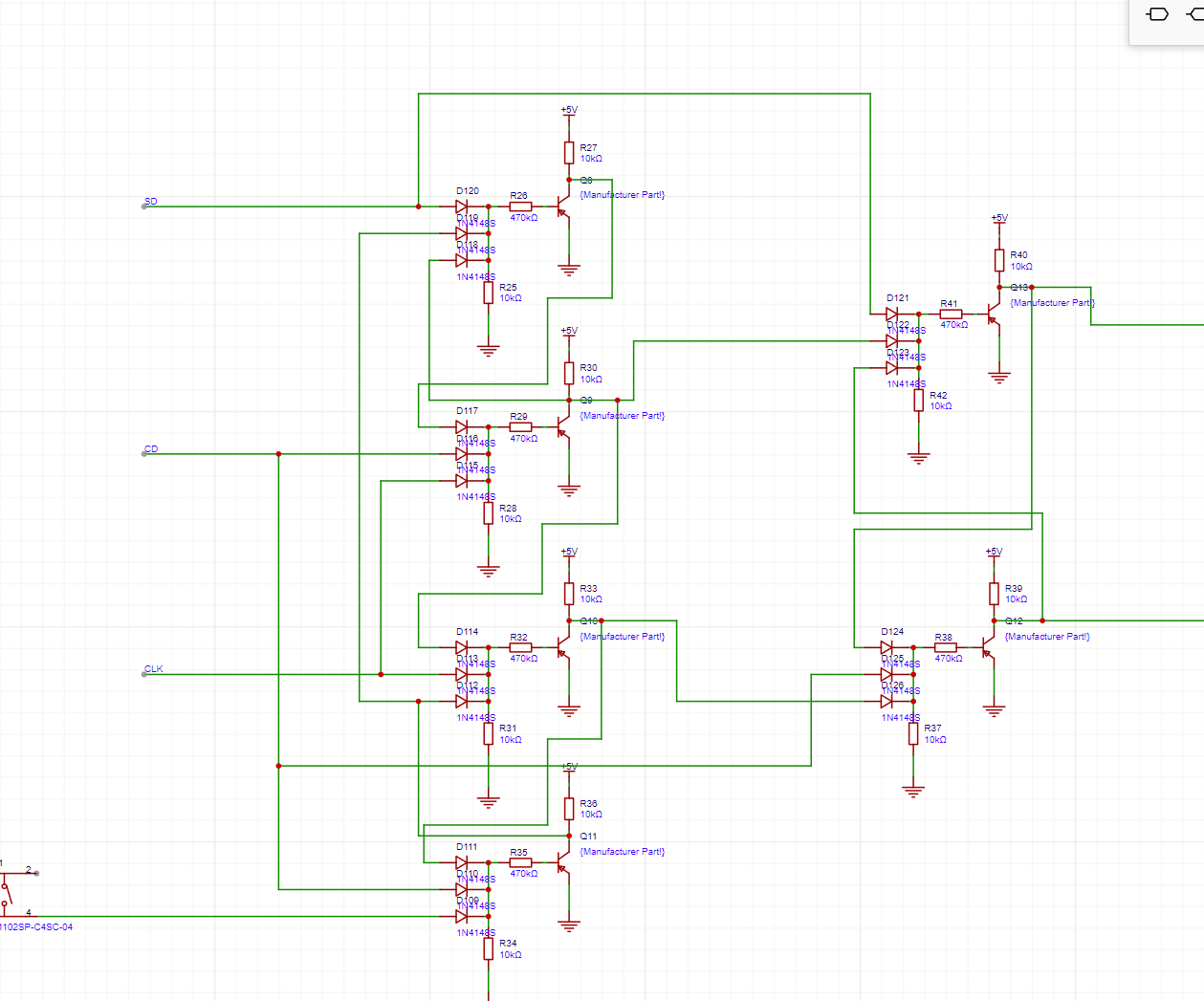

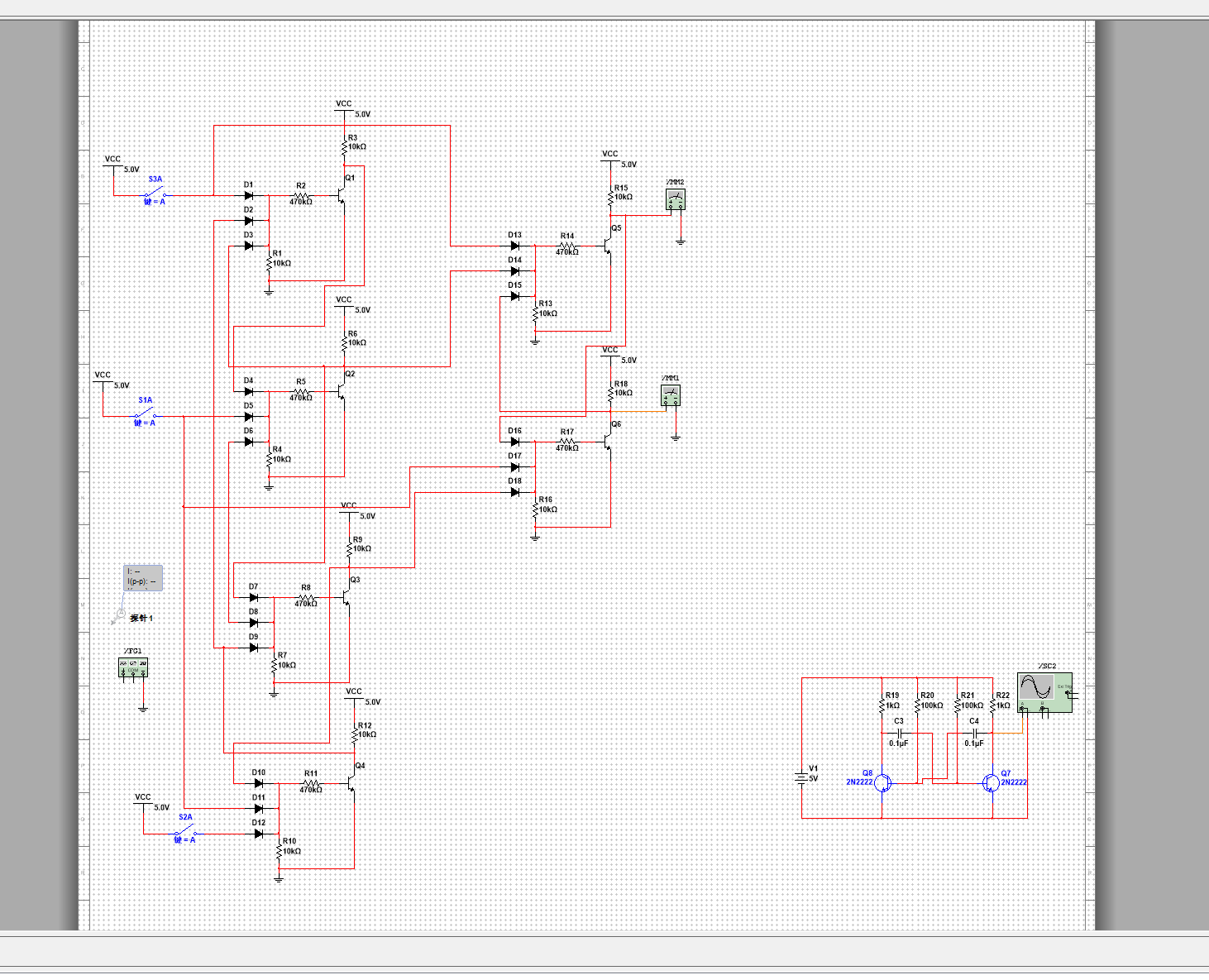

经过一番资料查阅和反复推演(主要是参考经典的分立元件触发器设计,并针对手头元件进行调整),我决定采用 “主从结构” 来实现边沿触发(更实用),核心由两个电平敏感的锁存器级联组成:

-

基本单元 - SR锁存器: 这是基石。我使用两个交叉耦合的 2N2222三极管 作为反相器,配合 1N4148二极管 和电阻构成基本的 与非门 或 或非门 结构,从而搭建出SR锁存器。这里二极管的引入是关键,用于实现逻辑“与”的功能。

-

门控逻辑: 在主锁存器和从锁存器的输入端,我需要用时钟信号

CLK来控制数据D的通路。这又需要用到由 1N4148二极管 和电阻构成的 与门(或者配合三极管构成更复杂的门电路),确保只有在时钟有效电平期间,数据才能进入相应的锁存器。 -

主从连接与反相: 主锁存器的输出需要通过受反相时钟控制的门电路连接到从锁存器的输入。为了实现时钟的反相,我还用了一个额外的 2N2222三极管 搭建了一个简单的 反相器。

-

输出缓冲: 从锁存器的输出端(Q 和 ~Q)通常也会加一级由 2N2222三极管 构成的反相器作为缓冲,增强驱动能力,并得到标准的输出极性。

-

电阻选择: 基极限流电阻、集电极上拉电阻、二极管逻辑中的电阻都需要精心计算和选择。我主要使用了 1KΩ, 4.7KΩ, 10KΩ 等常见阻值的碳膜电阻。电阻值的选取对三极管的饱和/截止状态、开关速度、功耗都至关重要,需要反复调整。(注:具体阻值取决于你的设计和工作电压,比如5V或3.3V)。

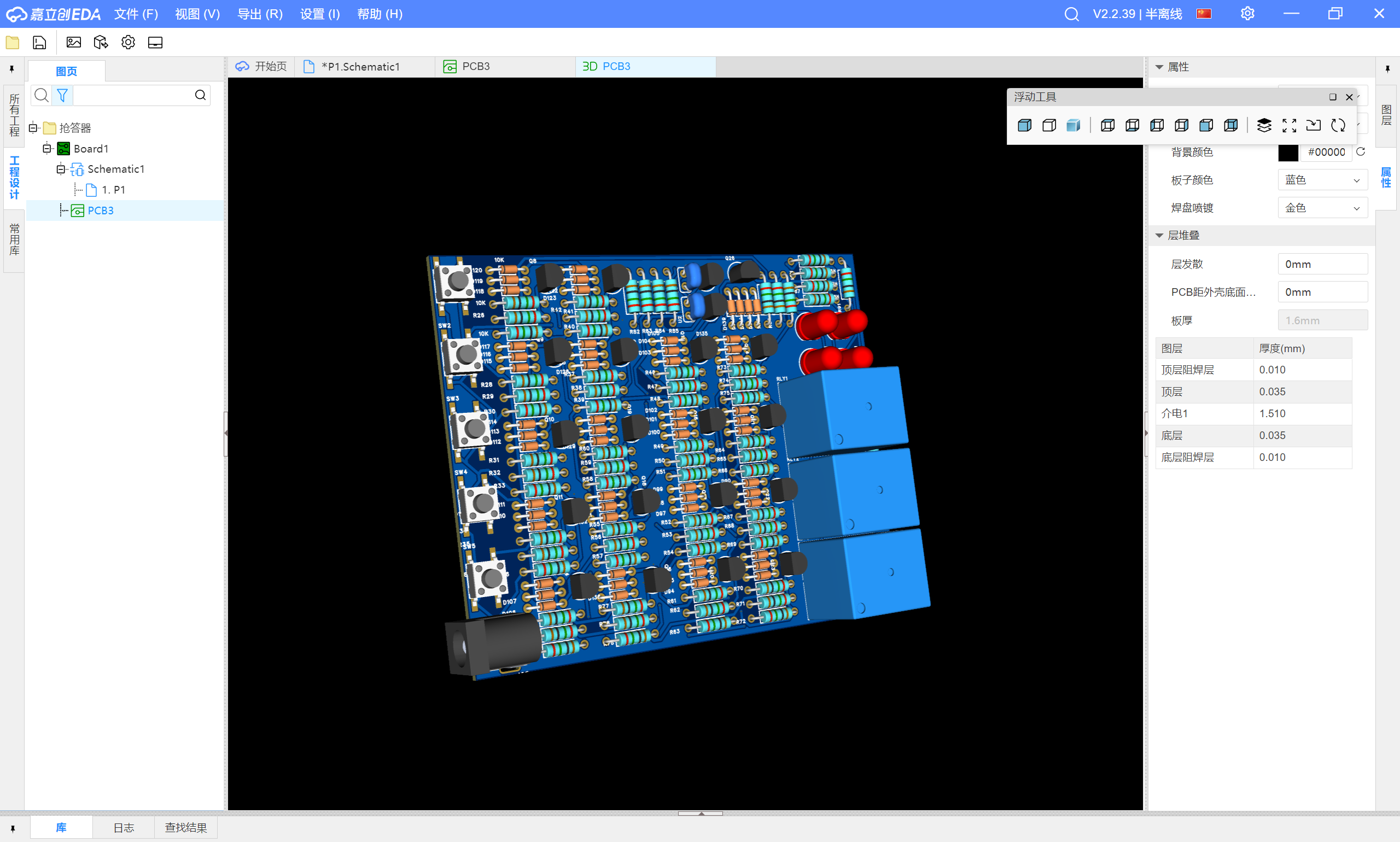

(示意图说明: 这里强烈建议你在文章中插入一张清晰的手绘或EDA绘制的电路图!这是文章的核心价值所在。由于文本限制,我无法直接绘图,但请务必补充上!图中需清晰标注所有元件:1N4148, 2N2222, 所有电阻值,连接关系,VCC, GND, CLK, D, Q, ~Q 引脚。)

搭建与调试 - 痛并快乐着

-

面包板上的舞蹈: 我选择在面包板上进行搭建。这一步需要极大的耐心!密密麻麻的跳线、二极管的方向、三极管的引脚(BCE)绝对不能错。每连接一部分,我就用万用表测量一下关键点的电压是否合理。

-

电源与信号: 使用稳定的 +5V直流电源 供电。时钟信号

CLK和数据信号D我使用了函数发生器来提供方波(频率先调低,比如1Hz-100Hz方便观察),或者直接用开发板的GPIO口手动控制。 -

初战不利 - 锁死或振荡: 第一次上电,结果往往不如人意。可能两个锁存器都锁死了(输出恒定高或低),或者在时钟边沿出现剧烈的振荡。这通常是因为:

-

时序问题: 主从之间的延迟不够或控制逻辑的时序配合不好。我在时钟路径上适当增加了小电容(几十pF到几百pF)来引入微小延迟,解决了大部分振荡问题。(注:这是分立元件电路常见技巧)。

-

电阻值不匹配: 重新计算和调整了部分基极电阻和上拉电阻,确保三极管能可靠地饱和导通和完全截止。

-

门电路逻辑错误: 仔细检查二极管构成的“与门”逻辑是否正确,是否存在信号短路或开路。

-

-

胜利的曙光: 经过多次修改电阻值、优化布线(减少杂散电容)、调整时钟频率后,奇迹出现了!我用示波器同时观察

CLK,D,Q:-

当

CLK上升沿(或下降沿,取决于设计)到来时,Q端稳定地锁存并输出了D端在时钟沿之前瞬间的值! -

在

CLK保持高电平或低电平期间,无论D如何变化,Q端都保持稳定不变! -

复位/置位功能(如果设计了)也能正常工作!

-

(图片/动图说明: 此处应插入示波器截图或屏幕录制!显示清晰的 CLK, D, Q 波形。重点展示时钟边沿处 Q 对 D 的跟随与锁存,以及时钟电平稳定期间 Q 的保持。这是最有力的证明!)

成功的喜悦与心得

看着示波器上那稳定跳变的 Q 波形,完美地跟随 D 在时钟边沿的变化并牢牢锁存,那一刻的成就感真的爆棚!这个用最朴素的1N4148和2N2222搭建起来的电路,实实在在地完成了D触发器的核心功能:在时钟边沿采样数据并存储!

这次实践让我深刻理解了:

-

数字逻辑的物理基础: 看似抽象的逻辑门和触发器,其底层就是二极管、三极管的开关组合。亲手搭建后,对“与”、“或”、“非”、“锁存”、“边沿触发”这些概念有了血肉般的认识。

-

时序的重要性: 分立元件电路中,门延迟、布线电容的影响被放大,时钟信号和数据信号的配合变得极其关键。解决振荡问题的过程就是对建立时间、保持时间概念的生动诠释。

-

调试的耐心与技巧: 从失败到成功,离不开系统性的调试:分模块验证、信号追踪、参数调整(电阻、电容)、利用好万用表和示波器。

-

基础元件的强大: 1N4148和2N2222这些“爷爷辈”的元件,依然能构建出复杂的数字逻辑功能,不得不佩服早期工程师的智慧。

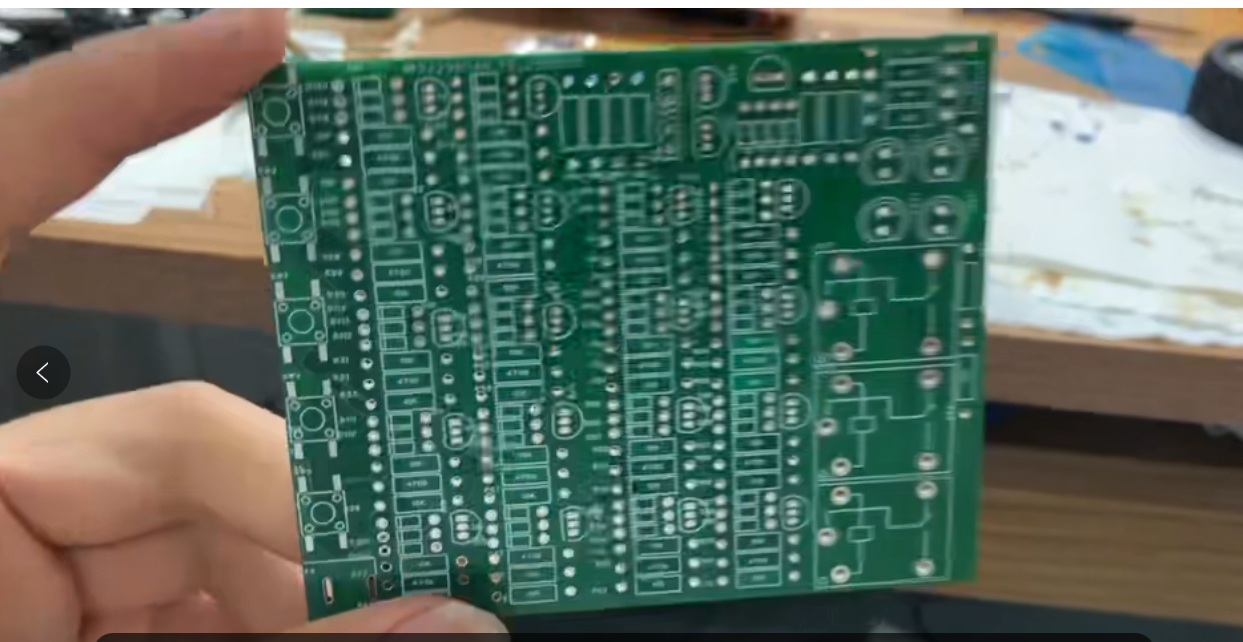

总结与资源

这次用分立元件(1N4148二极管 + 2N2222三极管 + 电阻 + 小电容)成功搭建D型触发器的经历,是一次极其宝贵的学习过程。它远超阅读书本或仿真带来的收获。我强烈推荐对数字电路底层感兴趣的朋友尝试一下!

重要提示:

-

我的电路图是核心!我会尽快整理好清晰的电路图分享给大家(或者评论区/资源链接提供)。

-

工作电压、具体的电阻值、是否使用小电容以及电容值,都需要根据你的实际设计和元件特性进行调整。没有绝对唯一的答案,调试是关键!

-

这个电路的速度和驱动能力当然无法与集成芯片相比,但其教学价值和探索乐趣是无价的!

如果你也尝试了或者有更好的分立元件触发器设计方案,欢迎在评论区一起交流探讨!共同进步!

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)