过冲、回沟、纹波问题分析(持续更新)

假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。如下图所示,设区域1阻抗为Z1,区域2

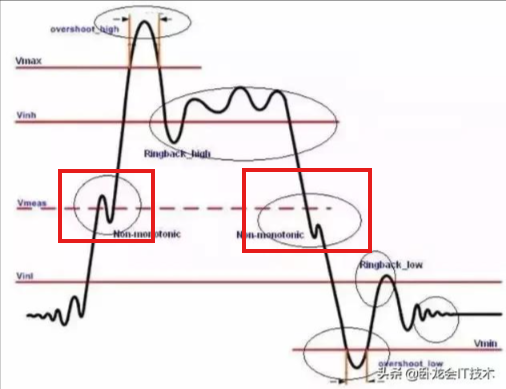

一.过冲

过冲是振铃的一部分,信号电平发生跳变后,第一个峰值电压或谷值电压超过设定的标准电压,主要表现为一个尖端脉冲。

一般描述过冲的影响,主要考虑:过冲的最大幅值、过冲的持续时间、过冲的发生频率这三个要素。

1.产生原因:

- 阻抗不匹配引起信号反射

- 驱动能力过强

- 信号串扰

阻抗不匹配:

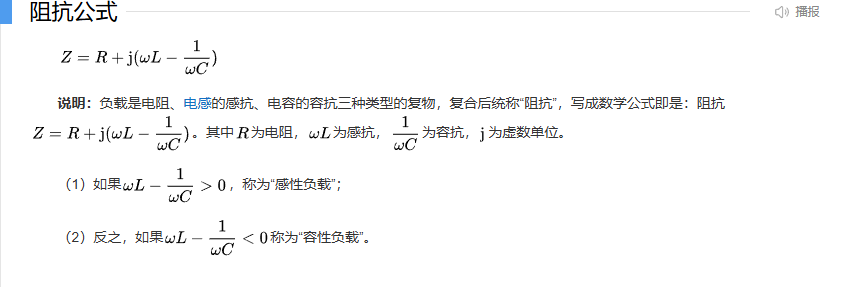

什么是阻抗?

在具有电阻、电感和电容的电路里,对电路中的电流所起的阻碍作用叫作阻抗。阻抗常用Z表示,是一个复数,实部称为电阻,虚部称为电抗,其中电容在电路中对交流电所起的阻碍作用称为容抗 ,电感在电路中对交流电所起的阻碍作用称为感抗,电容和电感在电路中对交流电引起的阻碍作用总称为电抗。 阻抗的单位是欧姆。阻抗的概念不仅存在于电路中,在力学的振动系统中也有涉及。

什么是阻抗匹配?

阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式,分低频和高频两种情况讨论。

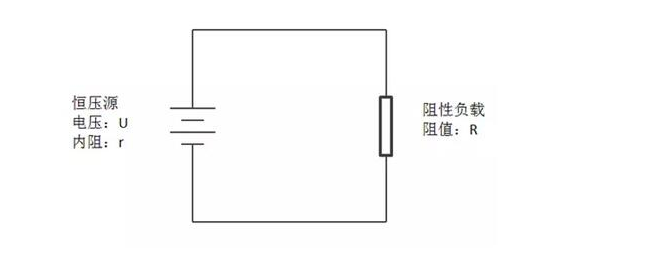

从直流电路/纯电阻的低频/高频电路入手:

如下图所示:假定激励源已定,那么负载的功率由两者的阻抗匹配度决定。对于一个理想化的纯电阻电路或者低频电路,由电感、电容引起的电抗值基本可以忽略,此时电路的阻抗来源主要为电阻。如图2所示,电路中电流I=U/(r+R),负载功率P=I*I*R。由以上两个方程可得当R=r时P取得最大值,Pmax=U*U/(4*r)。

当交流电路中含有容性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫作共扼匹配。

低频:

在低频电路中,一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。

阻抗匹配分为低频和高频两种情况讨论。当传输线的物理长度(L)接近信号波长(λ)的 1/10 或 1/20 时,就必须考虑传输线效应和阻抗匹配。

一般区分高频和低频的关键不是信号的绝对频率,而是信号的边沿速率(Rise Time/Fall Time) 以及其与传输线电气长度的关系。

以手机为例子:

| 信号类型 | 典型代表 | 是否需要阻抗匹配 | 主要原因 |

|---|---|---|---|

| 射频信号 | 5G, Wi-Fi, Bluetooth, GPS 天线馈线 | 必须 | 频率极高,波长极短,任何不匹配都会导致严重反射和功率损耗。 |

| 高速串行接口 | MIPI, PCIe, USB 3.x, LPDDR 数据/时钟线 | 必须 | 数据速率极高(Gbps),边沿速率极快(ps级),传输线效应显著。 |

| 高速时钟 | 高速总线参考时钟 | 必须 | 边沿陡峭,容易产生振铃和 overshoot。 |

| 电源网络 | VDD_CPU, VDD_MEM 等 | 不需要 | 直流/低频,重点是载流能力和电源完整性(去耦)。 |

| 模拟音频 | 耳机输出,麦克风输入 | 不需要 | 频率很低,波长很长,重点是抗干扰和屏蔽。 |

| 低速控制/调试接口 | I2C, SPI, UART, GPIO, 中断线 | 通常不需要 | 边沿速率慢,传输延时相对可以忽略。但长电缆连接时可能需要考虑。 |

博主是做传感器的,传感器一般就不用考虑,哈哈哈哈。

高频:

在高频电路中,还必须考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射。

什么是特征阻抗?

特性阻抗是均匀传输线上各点的电压与电流的比值。特性阻抗与传输线的物理结构有关,主要受介电常数、传输线到参考层的距离、线宽、线厚以及线间距影响。

为什么不匹配会发生反射?

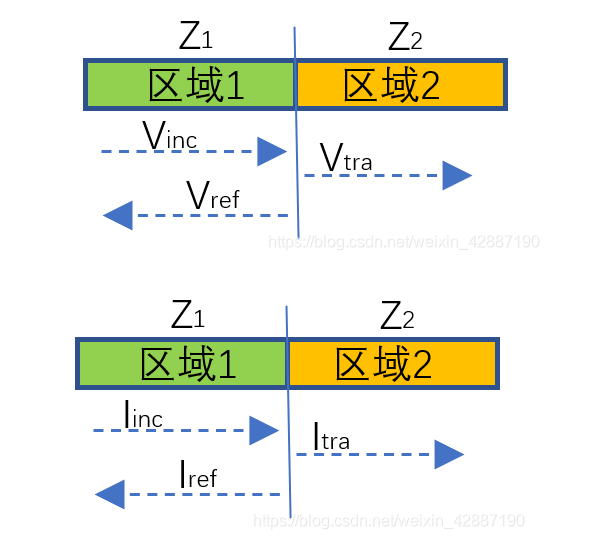

如下图所示,设区域1阻抗为Z1,区域2阻抗为Z2,信号经过两个阻抗不同的区域,在交界处处,电压和电流不能产生突变(若电压不连续,将产生无穷大的电场;若电流不连续,将产生无穷大的磁场)。

若Z1 ≠ Z2,则关系式 V1 =I1 ×Z1 ; V2 =I2 ×Z2 无法同时满足电压和电流连续的条件V1 = V2,I1 = I2 ,故只能从电磁波反射的角度进行分析,如下所示。

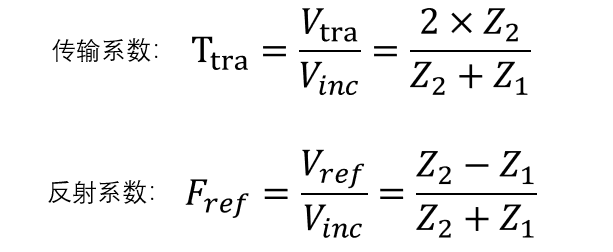

分界面两侧的电压相等,有 Vinc + Vref = Vtra ;

分界面两侧的电流相等,有Iinc - Iref = Itra ;

再有 Iinc × Z1 = Vinc ;Iref × Z1 = Vref ;Itra × Z1 = Vtra ;

由以上5个等式可以推导得出:

举个例子:

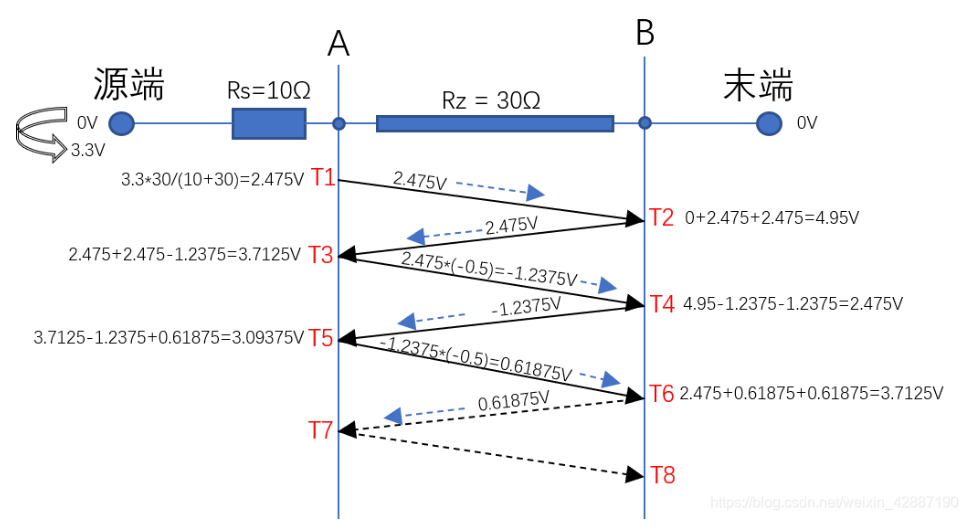

设传输线阻抗Rz=30Ω,源端串接的匹配电阻Rs=10Ω,则传输线左端A点反射系数为 (10 - 30)/(10 + 30) = -0.5,右端B点反射系数为 (+∞ - 30)/(+∞ + 30) = 1。

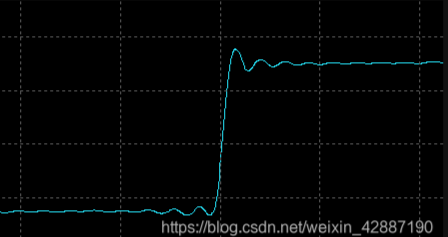

设初始状态都为低电平0.0V,T0时刻源端跳变为3.3V,发送逻辑高电平信号,末端B点的电压变化如下。

在理想情况(无损传输)下,信号会在传输线A、B两端无休止的反射振荡,反射电压的幅值越来越趋近于0,在实际中信号在传输过程中有衰减,最终趋于稳态。

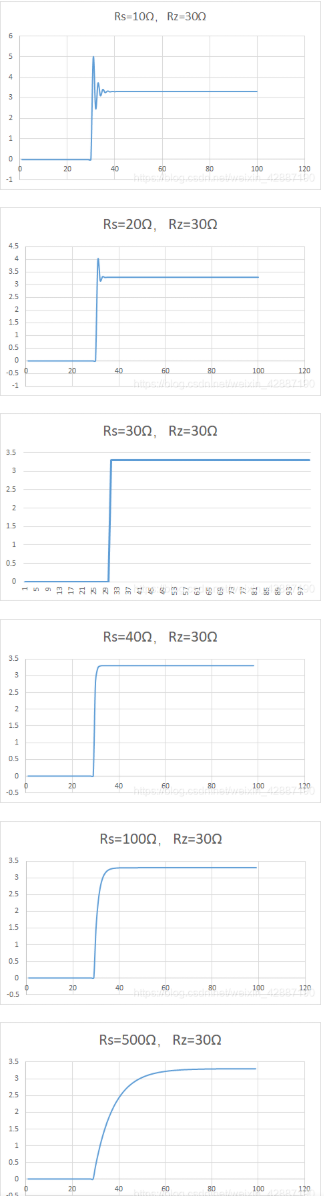

通过改变源端匹配电阻 Rs 的阻值,得到如下一部分模拟数据:

可以发现,当源端电阻小于传输线电阻时,信号变化比较快(上升时间较短),但是会伴随着过冲的产生,影响信号的完整性;

当源端电阻大于传输线电阻时,信号上升相对比较平缓,能有效解决过冲问题,但是增大了上升时间,限制了信号的传输速度;

驱动能力过强:

如上文所述,为什么传感器通信线路通常是低频的,没有这种反射问题,还会有过冲、振铃这些问题?

类比:开跑车撞墙

想象一下,你开着一辆动力极强的跑车(强驱动源),以极高的速度冲向一堵坚固的墙(负载电容,尤其是容性负载)。

-

猛踩油门(强驱动):引擎瞬间输出巨大马力(提供极大的瞬间电流

I = C * dV/dt),让车飞速前进(电压快速上升)。 -

撞墙瞬间(电压达到目标值):车的速度(电压)已经达到甚至超过了你的目标值,但由于巨大的动量(惯性),它根本无法瞬间停下。

-

结果:车头会严重撞瘪(过冲,Overshoot),整个车身可能会弹回来甚至晃动几下(振铃,Ringing),最后才瘫停下来。

从电路角度深入解释

-

负载的“惯性”:电容

电路中最大的“惯性”来源就是电容。无论是寄生的PCB走线电容,还是接收端芯片的输入电容,它们都遵循一个物理定律:电容两端的电压不能突变。给电容充电需要时间和能量。 -

驱动源的“力量”:输出阻抗

“驱动能力强”的输出级(比如CMOS数字输出),意味着它的输出阻抗(Rout)非常低。-

你可以把它想象成一个内阻极小的、功率巨大的电压源,它能提供非常大的电流。

-

-

冲突的发生

-

当信号需要从低电平跳变到高电平时,强驱动源以其极低的输出阻抗,极快地“泵出”巨大的电流,试图给负载电容充电。

-

由于电流极大 (

I很大),根据充电公式dV/dt = I / C,电压的变化率dV/dt极大,导致电压上升沿非常陡峭。 -

当电压快速达到目标值(比如3.3V)时,负载电容由于“电压惯性”,会继续吸收电流,试图让电压继续升高。

-

强大的驱动源此时依然在全力输出,因为它要维持这个电压值。于是,电压会冲过目标值,这就是过冲(Overshoot)。

-

-

振铃的由来:LC谐振

-

电路中的寄生电感(L)(来自走线、引脚等)和负载电容(C) 形成了一个LC谐振电路。

-

过冲的那部分能量(动能)并没有消失,而是被储存到了电感的磁场中。

-

随后,电感会释放能量,反过来给电容放电,导致电压下降。

-

然后电容又给电感充电,如此往复,能量在电感和电容之间来回交换,就形成了振铃(Ringing)。

-

由于电路中总存在一些电阻,这个振荡会逐渐衰减,最终稳定在目标电压。

-

信号串扰:

串扰导致过冲的原理与之前讲的直接驱动过冲不同,它是一种 “偷袭”机制。

串扰主要分为两类:容性串扰 和 感性串扰。它们都能导致受害网络(Victim Net)出现意外的过冲。寄生参数参考:寄生电容、寄生电感

容性串扰(电场耦合):

两根相邻的走线之间会形成寄生电容(Cm)。当 aggressor(攻击网络)上的信号快速跳变时(dV/dt 很大),变化的电场会通过这个寄生电容 “注入”电流 到 victim(受害网络)上。

如何导致过冲:

-

如果 victim 网络是一条传输线(例如一端是驱动源,另一端是高阻输入),这条线有特征阻抗 Z0。注入的电流会在 victim 线上向两端传播,形成串扰脉冲。

-

如果这个脉冲传播到远端的高阻输入端(开路),会发生全反射,反射电压与入射电压叠加,很容易形成一个超过电源电压的过冲脉冲。

-

即使 victim 不是传输线,注入的电流也会在 victim 的负载上产生一个意外的电压毛刺,如果这个毛刺的峰值超过了稳态电平,就表现为过冲。

感性串扰(磁场耦合):

两根相邻的走线的电流回路会形成相互耦合的寄生电感(Lm)。当 aggressor 上的电流快速变化时(dI/dt 很大),变化的磁场会在 victim 网络上 “感应”出电压。

如何导致过冲:

-

根据法拉第电磁感应定律,感应电压

-

如果 aggressor 的信号边沿非常陡峭(

dI/dt极大),感应出的电压会非常高。 -

这个感应电压会直接叠加在 victim 网络原有的信号上。如果 victim 原本是稳定的高电平,一个正的感应电压会使其超过原有的高电平,形成过冲。如果 victim 是低电平,一个负的感应电压会使其下冲(Undershoot)。

2.消除过冲方法:

1.调整驱动强度(最应该优先尝试的方法)

这是最有效且通常成本最低的方法。如果振铃源于驱动源过于“强大”,那么把它变得“温和”一些即可。

-

是什么:很多现代的数字芯片(MCU、FPGA、传感器、驱动器)的GPIO或输出引脚都支持可配置的驱动强度(Drive Strength) 或 ** slew rate(压摆率控制)**。

-

怎么做:通过芯片的配置寄存器或软件,将输出引脚的驱动强度从

最强调低为中等或弱。或者,如果支持,降低信号的压摆率(让边沿变得平缓一些)。 -

为什么有效:降低驱动强度相当于增加了驱动源的输出阻抗(Rout)。这增加了RLC电路的阻尼系数,有效抑制了由寄生电感和负载电容引起的谐振。更平缓的边沿意味着更少的谐波分量,从而从源头避免了激发谐振。

2. 添加并联电容(RC低通滤波效应)(常用)

如果无法在驱动端串联电阻,可以尝试在接收端并联一个电容到地。

-

是什么:在接收端(振铃信号的目的地)的输入引脚处,添加一个小的并联电容(Cshunt),例如 10pF 到 100pF。

-

怎么做:找到接收芯片的输入引脚,将一个小电容的一端连接到此信号线,另一端连接到良好的地。

-

为什么有效:

-

低通滤波:它和走线的特征阻抗(或驱动源的输出阻抗)形成了一个RC低通滤波器,可以滤掉导致振铃的高频噪声分量。

-

改变谐振点:它增加了总的负载电容(CL),从而改变了RLC电路的谐振频率 ,虽然更大的电容可能会让上升沿略微变缓,但它通常会显著降低谐振电路的Q值(品质因数),从而有效地抑制振铃的幅度。

-

-

注意:这会增加负载,可能使上升/下降沿变慢,需要评估是否满足时序要求。

3. 使用磁珠(Ferrite Bead)

磁珠在高频下表现为一个电阻,在低频下电感很小,不影响信号。

-

是什么:选择一个在振铃频率附近有高阻抗的磁珠,将其串联到信号路径中。

-

怎么做:将磁珠串联在驱动端和走线之间,或者接收端之前。

-

为什么有效:磁珠在特定的谐振频率点会呈现高阻抗,像是一个频率选择性的电阻,可以有效地吸收该频率的能量(即振铃能量),而对直流和低频信号阻抗很小,影响不大。

-

注意:这本质上是一种频率敏感的“串联电阻”,需要仔细选型。

4. 调整电源完整性

有时振铃并非来自信号路径本身,而是通过电源网络耦合过来的。

-

是什么:检查驱动芯片和接收芯片的电源引脚是否得到了充分的去耦。

-

怎么做:在尽可能靠近驱动芯片和接收芯片电源引脚的地方,添加不同容值的去耦电容(例如100nF + 10uF),以确保电源阻抗在很宽的频率范围内都很低。

-

为什么有效:一个不干净的电源会导致输出信号不稳定。改善电源完整性可以从源头减少信号的噪声,有时能间接改善振铃。

5. 最后的手段:软件/逻辑层面补偿

如果所有硬件手段都无效,且振铃已经导致系统误操作,可以考虑软件方式。

-

是什么:在读取信号时,增加一段延迟(De-bounce)或采样等待时间。

-

怎么做:在信号跳变后,等待振铃完全平息(例如等待几百纳秒到微秒)再去读取接收端的状态。

-

为什么有效:这回避了问题而不是解决它,但作为一种补救措施,它可以保证系统的功能正常。缺点是会降低系统响应速度。

二.回沟(待续)

与过冲类似,只不过是出现的时机,一个是在高低电平上,一个是在上升/下降沿。

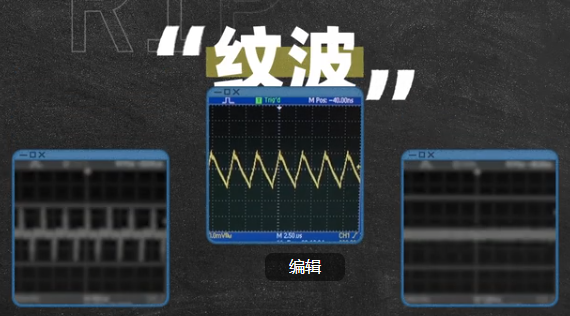

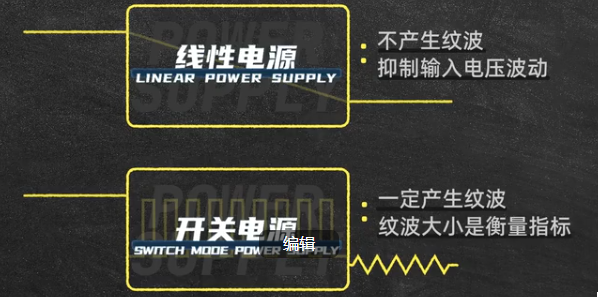

三.纹波(待续)

纹波是由于直流稳定电源的电压波动而造成的一种现象,因为直流稳定电源一般是由交流电源经整流稳压等环节而形成的,这就不可避免地在直流稳定量中多少带有一些交流成分,这种叠加在直流稳定量上的交流分量就称之为纹波。

下图中间这种才能称为纹波:

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)