STM32时钟系统

STM32时钟系统采用树状结构,分为高速和低速两大分支。高速时钟系统(HSI/HSE→PLL→SYSCLK)驱动CPU、总线等核心模块,频率达MHz级;低速时钟系统(LSI/LSE)则为RTC、看门狗等提供kHz级低频支持。两者通过RCC模块协调,高速系统侧重性能,低速系统专注低功耗,共同确保MCU在不同工作模式下的稳定运行。理解时钟树结构是优化系统性能和功耗管理的关键。

前言

在 MCU 中,“时钟”指的是一种持续振荡的信号(通常为方波),其周期决定了 CPU 执行指令的速度以及外设运行的节奏。就像人的心跳维持生命节奏一样,时钟信号维系着 MCU 的整个系统运行。

对于 STM32 而言,系统中的一切活动都离不开时钟信号。无论是 CPU,还是 定时器、串口、ADC、DMA 等外设模块,都必须依靠时钟驱动才能正常工作,掌握时钟系统,才能理解外设初始化、功耗优化、通信速率、系统稳定性等核心问题。学习时钟系统的过程,实际上就是理解 STM32 的节奏与生命源。

- 没有时钟 → 程序无法执行

- 时钟异常 → 系统运行紊乱或通信失败

为便于理解,本文将以 简化的方式 介绍 STM32 的时钟树结构,重点帮助读者掌握其工作原理与整体架构,而非在细节上做到完全还原。

1 STM32时钟树概述

STM32 的时钟系统采用 时钟树(Clock Tree) 的设计结构,这是一种层次化的体系,用于描述时钟信号如何从源头(内部或外部时钟源、PLL 等)生成、分配与分频,最终驱动微控制器的各个模块(如 CPU、外设、总线等)。这种设计直观地展示了时钟信号的流向与配置逻辑,是理解 STM32 时钟体系的核心工具。

在实际应用中,不同模块对时钟频率的需求不同,STM32 的时钟系统根据频率和用途分为高速时钟系统和 低速时钟系统。高速时钟用于驱动高性能组件(如 CPU 和 AHB 总线),而低速时钟用于低功耗或低频外设(如 RTC)。

2 高速时钟系统

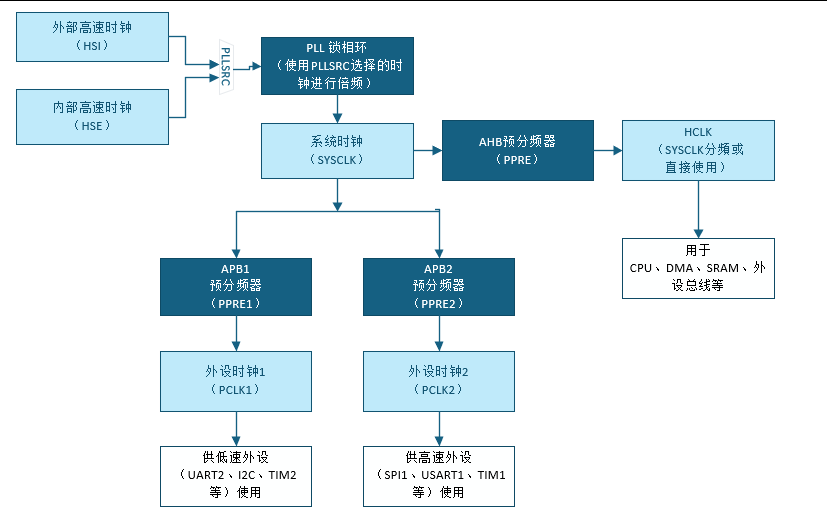

高速时钟系统主要负责驱动需要高性能的模块,如 CPU、内存、DMA 和外设。它的核心特点是频率较高(通常在 MHz 级别),由 HSI、HSE 或 PLL 生成。图1是STM32高速时钟系统示意图。

图1 STM32高速时钟系统简化结构示意图

图1 STM32高速时钟系统简化结构示意图

系统组成

-

时钟源:

-

HSI(High-Speed Internal Oscillator):内部高速振荡器,其典型频率因STM32系列而异,例如STM32F0/F1/F3系列为8 MHz,STM32F4/L0/L1系列为16 MHz,而STM32H7系列为64 MHz。

-

HSE(High-Speed External Oscillator):即外部高速晶振,频率范围通常在 4–26 MHz 之间(常见设计为 8 MHz 或 25 MHz)。使用外部晶振可为系统提供更高的时钟精度和稳定性,适用于对定时或通信速率要求较高的应用场景。

-

PLLSRC:即锁相环输入源,用于指定 PLL(锁相环)电路 从哪个时钟信号获取输入频率。该设置决定了 PLL 的基准时钟来源,从而影响后续倍频与系统主时钟的生成。

-

-

PLL(锁相环): 倍频从 HSI或HSE 获得的高频时钟, PLL 输出通常用于系统时钟SYSCLK。

-

SYSCLK(系统时钟):系统主时钟,由PLL 输出,频率通常较高(常见的 STM32H743 系列最高主频为 480 MHz), 作为高速时钟系统的核心,分配到各分支。

-

HCLK(AHB 时钟): 由 SYSCLK 通过 AHB 预分频器生成,是驱动 CPU 内核、DMA、总线矩阵以及 SRAM 等高速外设 的主系统时钟,其频率范围取决于具体的芯片系列和内核性能。

-

PCLK1/PCLK2(APB 时钟):由 SYSCLK 通过 APB1和APB2 预分频器(PPRE1、PPRE2)生成,频率通常低于 HCLK,其中:

- APB1(Advanced Peripheral Bus 1)低速外设总线,挂载外设USART2/3、UART4/5、I2C1/2/3、SPI2/3、CAN、DAC、TIM2~TIM7 等定时器

- APB2(Advanced Peripheral Bus 2)高速外设总线,挂载外设ADC1~3、SPI1、USART1、TIM1、TIM8(高级定时器)、

GPIOA~E(部分系列)、SYSCFG、EXTI

系统特点

- 高频率:MHz 级别,适合实时处理、数据传输等。

- 高性能:驱动 CPU 和高速总线(如 AHB)。

- 高功耗:频率越高,功耗越大,需优化分频设置。

3 低速时钟系统

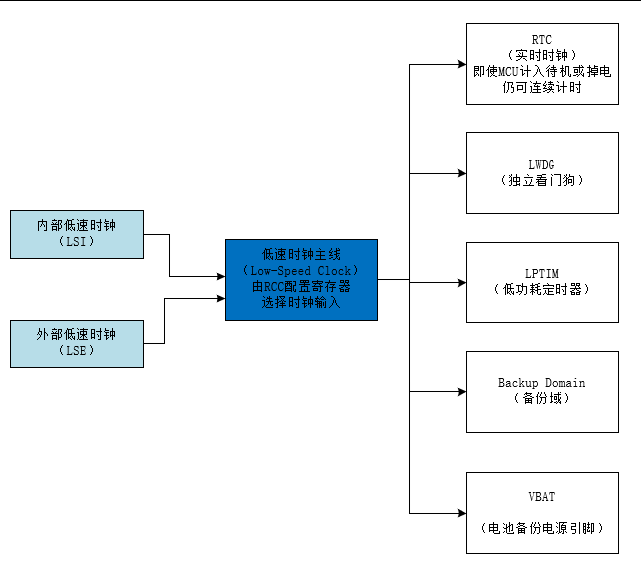

低速时钟系统频率通常在 kHz 级别,用于为低功耗和低频需求的模块(RTC、IWDG、LPTIM 等)提供可靠的低频时钟支持,使 MCU 能在各种低功耗场景中稳定运行。低速时钟系统是STM32 在“掉电仍能计时、崩溃仍能复位、休眠仍能唤醒”的关键基础。

图1是 STM32低速时钟系统(Low-Speed Clock System) 的简化结构示意图,展示了低速时钟源与各模块之间的关系。

图2 STM32低速时钟系统简化结构示意图

系统组成

-

时钟源:

- LSI(Low-Speed Internal Oscillator):内部低速振荡器,典型频率为 32 kHz(如 STM32F4 的 LSI 为 32 kHz),精度较低。

- LSE(Low-Speed External Oscillator):外部低速晶振,通常为 32.768 kHz,精度高,常见于 RTC。

- Low-Speed Clock(低速时钟主线): 是 LSE 和 LSI 时钟源的“汇聚层”, 可以通过 RCC 配置寄存器(RCC_BDCR)选择哪一个作为后面模块的时钟输入。 起到“时钟分配器”的作用,类似于 PLLSRC 的选择逻辑。

-

RTC 实时时钟:

实时时钟(RTC),可持续计时,用于时间计数、日历功能等。可由 LSE 或 LSI 提供时钟,频率固定为 32.768 kHz。 当MCU 进入待机或掉电,系统自动切换为VBAT 供电,RTC 仍可工作。 -

IWDG 时钟:

独立看门狗(IWDG),使用 LSI 作为时钟源(独立于主系统时钟), 即使主系统时钟出错,IWDG 仍能复位 MCU,防止系统死循环或崩溃。 -

LPTIM(Low Power Timer):

低功耗定时器(LPTIM),用于在低功耗模式下定时唤醒 MCU, 可选用 LSI 或 LSE 作为时钟源(经过分频)。 -

Backup Domain(备份域):

Backup Domain 是 STM32 在掉电或低功耗下仍能保持的“记忆区”,它保存 RTC 时间、用户自定义数据、以及时钟配置,由 VBAT 供电以保持独立运行。 -

VBAT(电池备份电源引脚):

为RTC、Backup Domain 提供独立电源,在主电源(VDD)断电时,保证计时和数据保持不中断。

高速时钟系统(HSE、HSI、PLL、AHB/APB 总线时钟等), 全部由 VDD 供电。一旦 VDD 断电,这些模块全部停止工作(包括 CPU、外设等)。

低速域(Backup Domain),当 VDD 断电但 VBAT 仍供电时,只有与 RTC、Backup Registers、 LSE 相关的部分电路还能运行。

系统特点

- 低频率:kHz 级别,典型为 32 kHz。

- 低功耗:适合电池供电设备或低功耗模式(如 Standby 模式)。

- 持续运行:即使芯片进入低功耗模式,低速时钟也能保持运行(如 RTC)。

系统应用

- 实时时钟(RTC)保持时间记录。

- 看门狗定时器防止系统死锁。

- 低功耗模式下的定时任务。

4 高速与低速时钟系统的关系

-

独立性:

- 高速时钟系统(HSI、HSE、PLL、SYSCLK、HCLK、PCLK)主要驱动主功能模块,运行在高频域。

- 低速时钟系统(LSI、LSE、RTC)独立运行,专注于低功耗和后台任务。

- 两者通过 RCC(Reset and Clock Control)模块协调,但互不干扰。例如,RTC 可在芯片休眠时继续运行,而 SYSCLK 和 HCLK 可关闭以省电。

-

选择与配置:

- PLLSRC属于高速时钟系统,用于选择 HSI 或 HSE 作为 PLL 输入,影响 SYSCLK 和 HCLK。

- 低速时钟系统也有类似的选择机制,如RCC 配置寄存器(RCC_BDCR) 选择 LSI 或 LSE。

-

时钟树中的体现:

- 在 STM32 时钟树中,高速时钟系统占据主干(HSI/HSE → PLL → SYSCLK → HCLK/PCLK),分支较多,复杂性高。

- 低速时钟系统是独立的小分支(LSI/LSE → RTC/IWDG),结构简单,频率固定。

-

功耗与性能:

- 高速时钟系统追求性能,频率高,功耗大。

- 低速时钟系统追求低功耗,频率低,适合后台任务。

5 时钟树中的高速与低速分类

在 STM32 的时钟树中,高速和低速时钟系统可以清晰分开:

- 高速时钟树:

- 路径:HSI/HSE → PLLSRC → PLL → SYSCLK → HPRE → HCLK → CPU/AHB/DMA。

- 路径:SYSCLK → PPRE1/PPRE2 → PCLK1/PCLK2 → UART/SPI/ADC。

- 频率:MHz 级别(如 16-480 MHz)。

- 低速时钟树:

- 路径:LSI/LSE → RTCSEL → RTC/IWDG。

- 频率:kHz 级别(如 32 kHz)。

总结

STM32 的时钟系统采用 时钟树(Clock Tree) 的设计结构,在这样的设计中高速和低速时钟系统可以清晰分开, 高速时钟系统追求性能,频率高,功耗大, 低速时钟系统追求低功耗,频率低,适合后台任务。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)